完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網技術文庫為您提供最新技術文章,最實用的電子技術文章,是您了解電子技術動態的最佳平臺。

對設計者很通常的情況是花費幾天或幾周的時間圍繞一個設計來滿足時序,甚至多半利用上面描述的自動種子變化,只面對可以起伏通過已有布局的小改變和時序特性完全改變。...

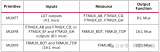

我們都知道,在7系列的FPGA中,每個CLB有兩個Slice;而在UltraScale系列中,每個CLB中只有一個Slice,Slice又分成了兩種類型SliceL(Logic)和SliceM(Memory),其中SliceM中的LUT可以當作分布式RAM來使用。...

在技術支持和維修方面,BYO通常缺乏立即可用的專業技術支持。這種情況通常需要依靠內部團隊的知識和技能,有時甚至需要尋求外部的咨詢服務,這可能導致問題解決的時間延長。...

所有代碼在典型的 FPGA 和主流 FPGA 供應商中都具有高度可重用性。 可以出于任何目的對文件進行重新混合、轉換和構建,甚至是商業用途。...

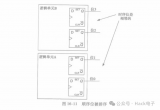

寄存器排序是布局工具把多位寄存器的相鄰位分組放進單個邏輯元件所利用的方法。大多數基于單元的邏輯元件有不止一個觸發器,因此,相鄰位放置在一起,時序可以被優化。...

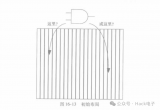

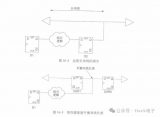

根據數據流的關系,我們可以采用單路徑延遲反饋(Single-pathDelay Feedback, SDF)運算單元流水結構,SDF單元如下圖所示。...

本項目主要在FPGA上實現了一個經典小游戲“俄羅斯方塊”。本項目基本解決方案是,使用Xilinx Zynq系列開發板 ZedBoard 作為平臺,實現主控模塊,通過VGA接口來控制屏幕進行顯示。...

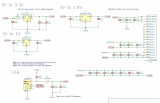

FPGAs需要多種不同的電壓。在這個設計中,將I/O引腳的工作電壓設置為3.3V(因為這對于業余愛好者來說比較標準),但還需要提供5V、1.8V和1.0V的電壓。這意味著需要處理4種不同的電壓!...

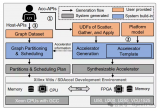

ThunderGP是基于HLS的開源通用圖形處理框架,支持Vitis和SDAccel開發環境,適用于U50、U200、U250和VCU1525等Xilinx Alveo平臺(官方開發板)。...

自上而下的設計是把系統模塊作為基本單元,然后再逐一分解,一直這樣分解下去,直到無法進一步分解,可以用EDA元件庫中的元件來實現為止。...

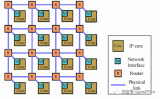

交換機根據所選拓撲采用在網絡節點之間路由信號的任務。請注意,NoC 的架構假設使用了一個相當強大的開關,這將提供最低水平的延遲(最多納秒)。...

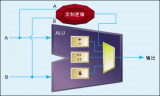

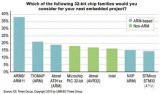

精簡指令集計算(RISC)架構的目標之一即是保持指令簡單化,以便讓指令運行得足夠快。這與復雜指令集計算(CISC)架構正好相反,后者一般不會同樣快地執行指令,但每個指令可完成更多處理任務。...

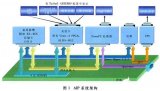

基于FPGA的單芯片實現方法具有低成本和快速面市等優點,是多芯片和ASICSoC非常有吸引力的替代方案...

轉換的依據是一個簡單的運算關系:“補碼的整數值”+“原碼絕對值的整數值”=2^B,B為位寬。比如帶符號數原碼1110的補碼為1010:1110取絕對值0110為6;1010為10,二者加起來為2^4=16。...

AIP架構的最新應用是獵戶座載人太空船的視覺處理單元(VPU)。VPU可為處理影像算法提供可重構的平臺,有利于位姿估計、光學導航以及壓縮/ 解壓縮。...

FPGA軟件包含進行設計而產生的程序、文檔和數據,同時包含與之相關的軟件特性和硬件特性。FPGA軟件測試需要考慮軟件代碼正確性、軟硬件接口協調性、時序性等方面的全面覆蓋。...

片內PLL設計是IC設計中的一個重要環節,在無線通信、高頻通信和數字通信等領域PLL的使用占據重要地位。本文以Cyclone IV系列EP4CE15F17C8N型FPGA為研究對象,其包含四個通用的PLL,分別位于芯片的四個邊角,采用獨立的2.5V電壓供電。...

ASIC中你可以直接加寬金屬線,比如兩倍寬度走時鐘線,復位線啦,之類的。金屬線寬度變大,線上的延遲變小,對速度也是有幫助的。...