完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

電子發(fā)燒友網(wǎng)技術(shù)文庫(kù)為您提供最新技術(shù)文章,最實(shí)用的電子技術(shù)文章,是您了解電子技術(shù)動(dòng)態(tài)的最佳平臺(tái)。

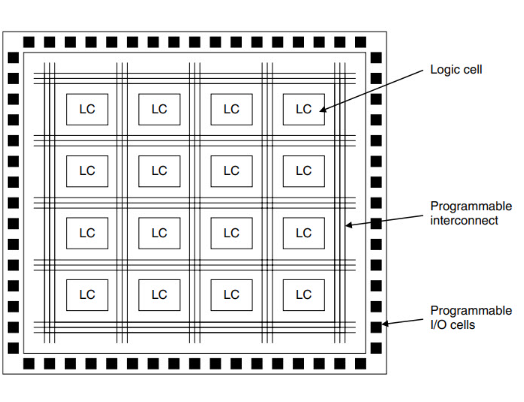

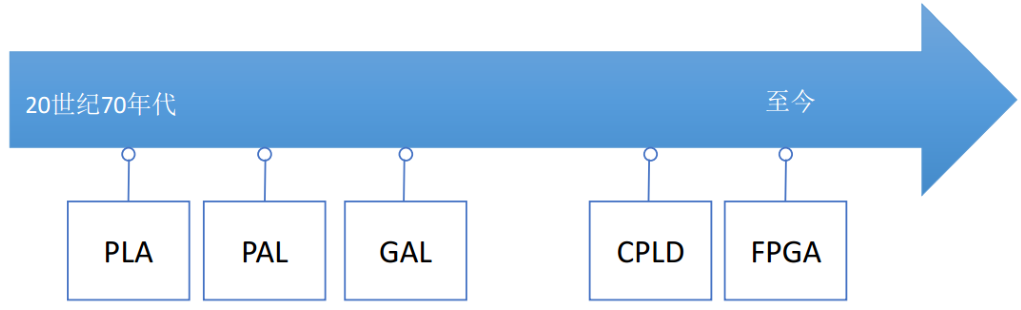

可編程邏輯器件包含多個(gè)邏輯元件,例如觸發(fā)器以及可由用戶配置的AND和OR門,用戶可以在使用專用軟件應(yīng)用程序完成的編程過(guò)程中修改內(nèi)部邏輯和連接。...

FPGA 在通信領(lǐng)域的應(yīng)用可以說(shuō)是無(wú)所不能,得益于 FPGA 內(nèi)部結(jié)構(gòu)的特點(diǎn),它可以很容易地實(shí)現(xiàn)分布式的算法結(jié)構(gòu),這一點(diǎn)對(duì)于實(shí)現(xiàn)無(wú)線通信中的高速數(shù)字信號(hào)處理十分有利。...

時(shí)鐘設(shè)計(jì)方案 在復(fù)雜的FPGA設(shè)計(jì)中,設(shè)計(jì)時(shí)鐘方案是一項(xiàng)具有挑戰(zhàn)性的任務(wù)。設(shè)計(jì)者需要很好地掌握目標(biāo)器件所能提供的時(shí)鐘資源及它們的限制,需要了解不同設(shè)計(jì)技術(shù)之間的權(quán)衡,并且需要很好地掌握一系列設(shè)計(jì)實(shí)踐知識(shí)。不正確的設(shè)計(jì)或次優(yōu)的時(shí)鐘方案可能會(huì)導(dǎo)致在最好情況下較差的設(shè)計(jì)性能,或者在最壞情況下的隨機(jī)和難...

對(duì)于最后一種情況,也就是位于中間白色區(qū)域的點(diǎn),他需要進(jìn)行雙線性插值。可以看到整個(gè)點(diǎn)位于第四個(gè)block,所以他需要在第一個(gè),第二個(gè),第四個(gè)和第五個(gè)block上分別計(jì)算直方圖均衡化的結(jié)果,和相應(yīng)的權(quán)重。...

可編程AES加解密IP內(nèi)建密鑰擴(kuò)展功能,使用初始密鑰產(chǎn)生擴(kuò)展密鑰,用于加解密過(guò)程。可編程AES加解密IP處理128-bit分組數(shù)據(jù),并且支持可編程的密鑰長(zhǎng)度:128-bit,192-bit和256-bit。...

對(duì)于數(shù)字設(shè)計(jì)人員來(lái)講,只要信號(hào)從一個(gè)時(shí)鐘域跨越到另一個(gè)時(shí)鐘域,那么就可能發(fā)生亞穩(wěn)態(tài)。我們稱為“跨時(shí)鐘域”即“Clock Domain Crossing”,或CDC。...

CPU、GPU遵循的是馮·諾依曼體系結(jié)構(gòu),指令要經(jīng)過(guò)存儲(chǔ)、譯碼、執(zhí)行等步驟,共享內(nèi)存在使用時(shí),要經(jīng)歷仲裁和緩存。 而FPGA和ASIC并不是馮·諾依曼架構(gòu)(是哈佛架構(gòu))。以FPGA為例,它本質(zhì)上是無(wú)指令、無(wú)需共享內(nèi)存的體系結(jié)構(gòu)。...

模擬有數(shù)十億個(gè)晶體管的現(xiàn)代SoC相當(dāng)耗費(fèi)資源,依芯片大小和復(fù)雜性,可能需要跨越多個(gè)機(jī)架、數(shù)十甚至數(shù)百個(gè)FPGA。...

FPGA 是一種偽通用計(jì)算加速器,與 GPGPU(通用 GPU)類似,F(xiàn)PGA 可以很好地卸載特定類型的計(jì)算。從編程角度上講,F(xiàn)PGA 比 CPU 更難,但從工作負(fù)載角度上講 FPGA 是值得的:和 CPU 基線相比,好的 FPGA 實(shí)現(xiàn)可以提供數(shù)量級(jí)的性能和能量?jī)?yōu)勢(shì)。...

Nitro DPU系統(tǒng)提供了密鑰、網(wǎng)絡(luò)、安全、服務(wù)器和監(jiān)控等功能支持,釋放了底層服務(wù)資源供客戶的虛擬機(jī)使用,并且NitroDPU使AWS可以提供更多的裸金屬實(shí)例類型,甚至將特定實(shí)例的網(wǎng)絡(luò)性能提升到100Gbps。...

據(jù)我了解,目前國(guó)內(nèi)很多大學(xué)是沒(méi)有開(kāi)設(shè)FPGA相關(guān)課程的,所以很多同學(xué)都是自學(xué),但是自學(xué)需要一定的目標(biāo)和項(xiàng)目,今天我們就去看看常春藤盟校Cornell University 康奈爾大學(xué)開(kāi)設(shè)的FPGA項(xiàng)目課程。...

并行處理是最普遍的,也是AI加速器的基礎(chǔ)。它可以通過(guò)許多陣列的小型專用處理內(nèi)核(如特定算法的GPU)來(lái)實(shí)現(xiàn),或者以數(shù)據(jù)流(即專用處理器的流水線)的方式來(lái)實(shí)現(xiàn)。...

接下來(lái)我們下載兩塊開(kāi)發(fā)板的測(cè)試程序,先在5CEFA7F23的下載器內(nèi)添加比特流文件,輸入翻轉(zhuǎn)率50%比特流文件并且加載。...

這里,我們基于多個(gè)互相同步的XCZU29DR FPGA板開(kāi)發(fā)了一個(gè)可擴(kuò)展系統(tǒng),每個(gè)單板擁有16個(gè)6.554GS/s的DAC通道和16個(gè)2.058GS/s的ADC通道,工作時(shí)無(wú)需模擬I/Q混頻器。...

從這個(gè)例子可以看到,如果一個(gè)信號(hào)被自動(dòng)移除了,應(yīng)當(dāng)首先應(yīng)當(dāng)考慮它是否沒(méi)有在別處被用到。不過(guò),在下一個(gè)例子里馬上可以看到這并不是信號(hào)被優(yōu)化掉的唯一的原因。...

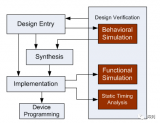

Verilog HDL是一種硬件描述語(yǔ)言,以文本形式來(lái)描述數(shù)字系統(tǒng)硬件的結(jié)構(gòu)和行為的語(yǔ)言,用它可以表示邏輯電路圖、邏輯表達(dá)式,還可以表示數(shù)字邏輯系統(tǒng)所完成的邏輯功能。...

DR3和RAM一樣,是一個(gè)存儲(chǔ)器件,它的每個(gè)內(nèi)部單元都存儲(chǔ)了當(dāng)前的數(shù)據(jù)狀態(tài)值。 但DDR3和RAM本身,是沒(méi)有“空”、“存有數(shù)據(jù)”,“數(shù)據(jù)滿”等概念的。只要給地址,它就會(huì)把當(dāng)前地址的數(shù)據(jù)給到總線上,而且這個(gè)地址可以讀很多次。...

Xilinx Vivado工具的配置約束隱藏得比較深,如圖1所示,在進(jìn)入配置頁(yè)面前,首先需要點(diǎn)擊PROGRAM AND DEBUG->Generate Bitstream執(zhí)行工程的全編譯,然后點(diǎn)擊IMPLEMENTATION->OpenImplemented Design進(jìn)入實(shí)現(xiàn)頁(yè)面。...

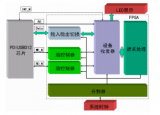

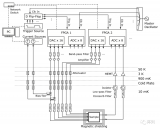

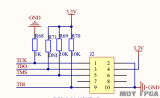

由于 PDIUSBD12 在讀寫時(shí)序上有時(shí)間限制,例如每次讀寫操作之間的間隔不能小于 500ns,而 FPGA 的系統(tǒng)時(shí)鐘一般頻率都比較高,所以不能直接使用系統(tǒng)時(shí)鐘控制 PDIUSBD12,必須進(jìn)行分頻。分頻器模塊的功能就是按照要求由系統(tǒng)時(shí)鐘生成所需頻率的時(shí)鐘信號(hào)。...