引 言

隨著移動通信的發展。通信網絡覆蓋范圍已經成為衡量通信網絡運行的重要標準,直接影響著運營商的經濟效益。而直放站的發展應用,已成為提高運營商網絡質量,解決網絡盲區或弱區問題,增強網絡覆蓋的主要手段之一。一個基站可以與幾個直放站相連,可以組成鏈狀、星型、樹型等靈活的拓撲結構,使基站的覆蓋范圍大大增加。同時,既節省空間,又降低成本,提高了組網的效率。

但由于傳統模擬直放站設備間沒有統一的協議規范,無法滿足系統廠商與直放站廠商的兼容,無法實現基站和直放站之間更有效的互通,從而限制了兩者之間控制和數據的可靠傳輸。2003年6年,由包括愛立信、華為、NEC、北電網絡及西門子5大集團合力制定了CPRI(Common Public RADIo Interface)接口。該組織成立的主要目的是制定這個接口的標準協議,從而使該接口成為一個公共的可用的指標。開放的CPRI接口為3G基站產品和2G數字直放站在增加效益,提高靈活性方面提供了便利。

1 CPRI協議概述

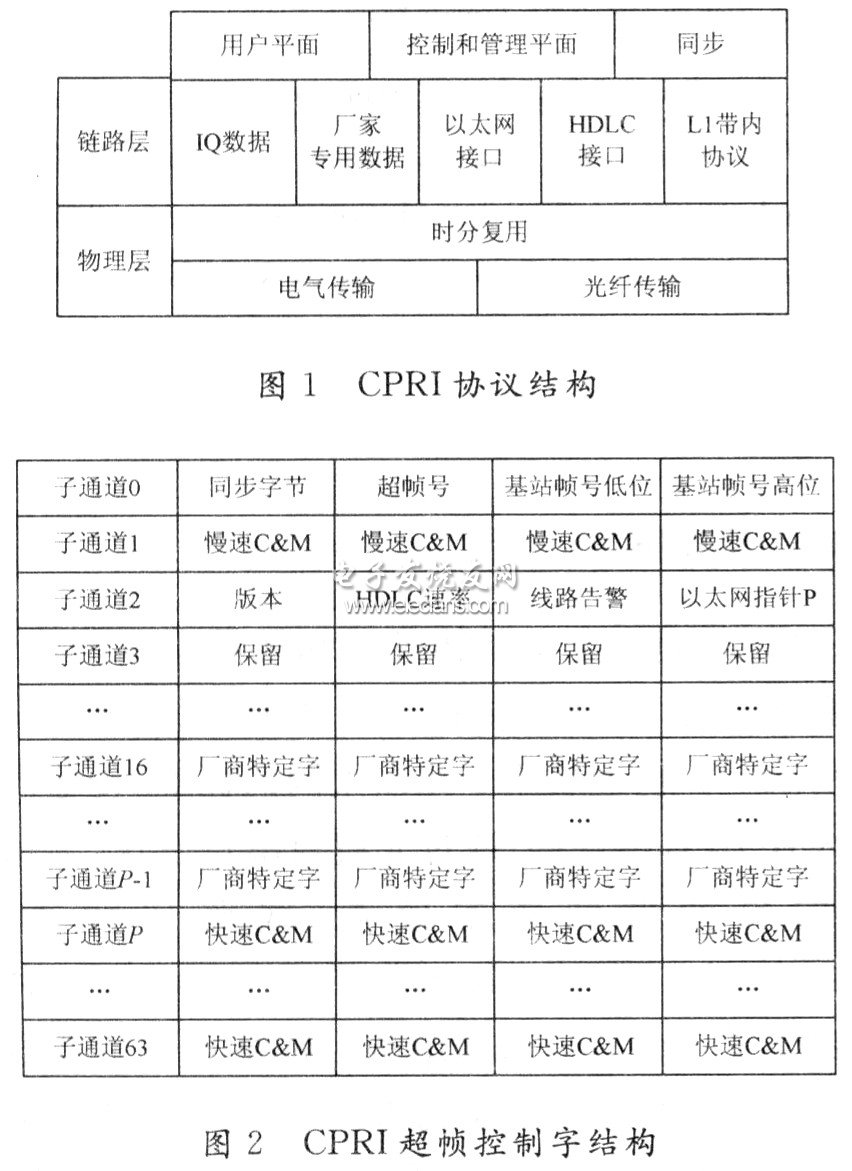

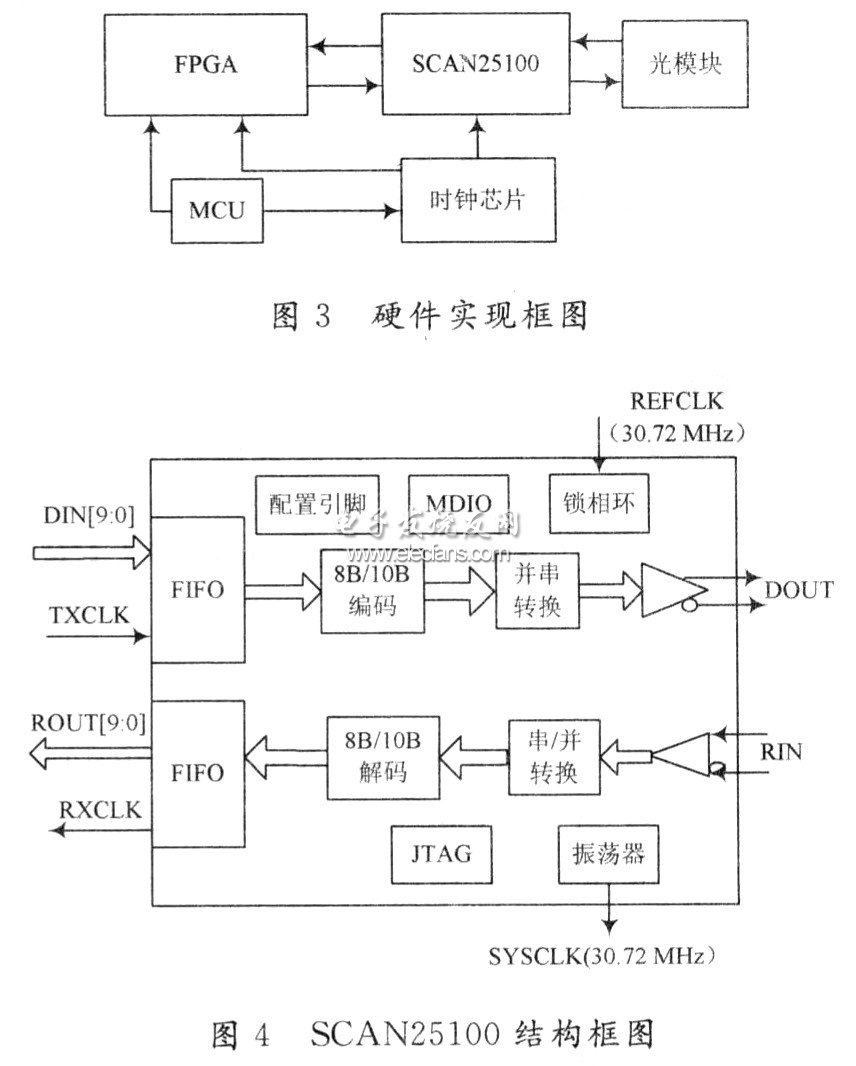

CPRI規范定義了物理層和鏈路層兩層協議,能實現數字基帶IQ信號傳輸時分復用,其協議結構圖如圖1所示。物理層用千兆以太網的標準,傳輸的數據采用8 B/10 B編解碼,通過光模塊串行發送,為達到所要求的靈活度和成本效益,線路比特速率有*.4 Mb/s,1228.8 Mb/s和2 457.6 Mb/s三種。鏈路層定義了一個同步的幀結構。幀結構包括基本幀和超幀,每個基本幀的幀頻為3.84 MHz,包括16個時隙,根據線路比特率的不同,每個時隙的大小分別為1 B。2 B,4 B。其中第一個時隙為控制時隙,其余15個時隙為I/O數據時隙,用來傳送I/O數據流。超幀則由256個基本幀構成,256個基本幀的控制時隙共同構成超幀的控制結構(如圖2所示),同時,定義了快速C/M通道(以太網)和慢速C/M通道(HDLC),用于傳送控制類和管理類的數據,可以對直放站進行維護。

?

?

?

2 硬件實現方案

2.1 方案對比

對于CPRI硬件實現方案,有以下幾種方案可以選擇:

(1)PMC方案。采用PMC7830或PMC7832芯片,這一類芯片把CPRI協議全部集成在芯片內部,只留出接口,使用簡單方便,可完全支持用于無線基站連接的公共射頻接口(CPRI)規范。

(2)用帶ROCKET IO的FPGA實現CPRI協議,此方法靈活性高,但開發時間周期會比較長,影響產品開發。

(3)FPGA與SCAN25100相結合。由FPGA實現CPRI的成解幀及相關接口設計,SCAN25100負責完成8 B/10 B編解碼和高速串并轉換。鏈路層的幀協議修改方便,而物理層則由芯片完成,使用簡單,性能穩定。開發成本較低,且擴展性好。

?? ? (4)FPGA與TLK4015相結合。TLK4015是4通道、0.6~1.5 Gb/s通道收發器,當系統需要多的通道數時,使用該方案可以減少電路板尺寸。

2.2 硬件詳細設計

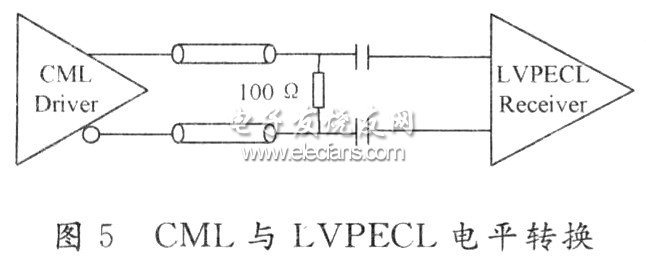

該設計采用第3種的硬件實現方案,整個硬件實現由5個部分組成,如圖3所示,分別為CPRI鏈路層協議實現模塊,CPRI物理層協議實現模塊、光傳輸模塊、時鐘管理模塊和系統配置與監控模塊。

?

?

?

2.2.1 CPRI鏈路層協議實現模塊

CPRI鏈路層只是定義了一個同步的幀結構,而里面的IQ數據和控制管理數據都是由用戶按需求自由處理的,采用FPGA實現CPRI的成幀、解幀及相關的控制,處理靈活,方便以后服務增加進行升級。在下面的軟件部分做詳細介紹。

2.2.2 CPRI物理層協議實現模塊

采用國半的CPRI串行/解串器SCAN25100。SCAN25100是專門為CPRI協議設計的高速串并轉換芯片,除了串并轉換之外,還有8 B/10 B編解碼功能,其內部結構框圖如圖4所示。

圖4中的TXCLK和RXCLK都是雙邊沿采集數據,降低了頻率要求,光纖接口(DOUT和RIN)的速率由TXCLK決定,當TXLCK為61.44 MHz時,經8 B/10 B編碼,再并串轉換后,DOUT的速率就是1 228.8 Mb/s。對于RXCLK也就是接收過程的時鐘,可以采用芯片內部自動恢復模式。當作為RE端時,內部振蕩器產生的30.72 MHz時鐘SYSCLK可以直接作為參考時鐘REFCLK,省去一個精準的外部時鐘,而且可以利用芯片上的兩個鎖相環路自動將遠程射頻單元同步到負責基帶處理工作的基站。當作為REC端時,需要由時鐘芯片產生30.72 MHz的時鐘給SCAN25100當參考時鐘。具體應用時,可以使用芯片的配置引腳進行芯片工作模式配置,也可以用MDIO接口對芯片內部寄存器進行編程,達到配置芯片的目的。

此外,該芯片還提供了延遲校準測量功能,通過讀內部相應的寄存器值,再進行簡單的換算后,就可以得到數據的傳輸延遲,其準確度達到±800 ps。SCAN25100很好地滿足CPRI物理層的功能,性能穩定,省去了8 B/10 B編解碼和接收端的時鐘恢復,減輕FPGA開發壓力。

2.2.3 光纖傳輸模塊

由于CPRI光口的傳輸速率有*.4 Mb/s,1228.8 Mb/s和2 457.6 Mb/s三種,所以光纖模塊應該選用多模光纖模塊,可以滿足3種速率的不同選擇。實現多塊單板之間的通信,形成鏈狀和星型混全組網,提高整個數字直放站系統的覆蓋范圍。

2.2.4 時鐘管理模塊

對于數字直放站系統,需要用到好幾個低抖動、低相位噪聲時鐘,如SCAN25100,FPGA等,而且電平有LVDS,LVPECL,CMOS等。時鐘是整個系統的核心,其性能直接影響整個系統的工作。

AD9516是一款將低相位噪聲時鐘發生和小于1 ps低抖動14通道時鐘分配功能集成在一起的時鐘集成電路。內部集成了1個整數n分頻的頻率合成器、2個參考輸入端、1個壓控振蕩器(VCO)、可編程驅動器、可調延遲線和14個時鐘驅動器,包括LVPECL,IVDS和CMOS三種電平模式輸出。由于片內集成了VC0,省去了外部振蕩器,同時也提高了系統設計的穩定性。3種電平模式時鐘輸出,豐富了接口方式,給系統設計提供了便利,因此,該系統中采用ADI的時鐘芯片AD9516。

2.2.5 系統配置及監控

利用單片機對時鐘芯片等進行初始化配置,與FPGA進行通信,實現相應的系統監控功能。

2.3 電路接口設計和PCB布板問題

2.3.1 接口電平

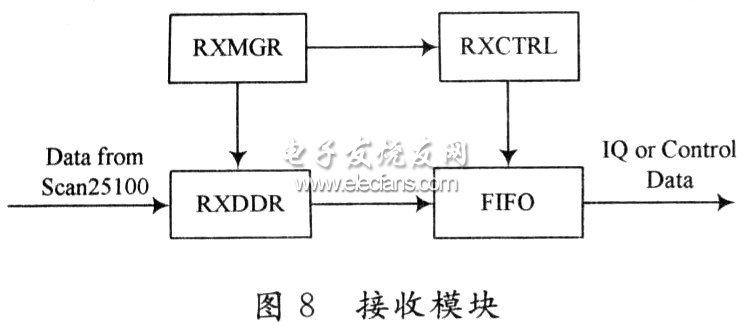

SCAN25100的串口輸出是CML差分電平模式,而光纖模塊的接口電平是LVPECL差分電平模式,為了實現穩定可靠工作,需要進行接口電平轉換,其接口轉換如圖5所示。

?

?

?

在該系統中,當CML差分輸出時,芯片已經在差分輸出加了電阻.而光纖模塊的LVPECL電平中已經有隔直電容,所以在處理兩者之間的接口電平時顯得十分簡單,可以把兩者直接相連就可以解決接口電平匹配問題。

2.3.2 PCB布板

由于是GHz級的設計,對PCB設計的要求較高.對高速差分布線,特別是光模塊和SCAN25100接口走線(圖4中的DOUT和RIN),應該盡量短且不同層布線,減少收發之間的串擾,增加回流過孔減少其他信號耦合,設計好高速差分走線的阻抗匹配,保證高速串行信號的完整性。

3 軟件實現

3.1 單片機

實現SPI通信協議.完成對時鐘芯片、A/D與D/A的初始化配置,使得時鐘芯片提供多路時鐘分別給FPGA.SCAN25100,A/D與D/A。實現I2C通信協議,完成單片機與FPGA之間的通信,從而對數字中頻進行設置及監控。實現485總線對整個系統進行監控。

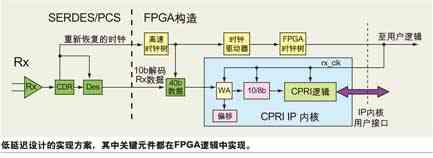

3.2 FPGA

主要是完成CPRI的鏈路層協議。主要分為3個模塊,發送、接收、CPRI啟動過程模塊。其結構如圖6所示,FPGA內部實現CPRI的成解幀和數字上下變頻(DDc及DUC.這里不在討論),發送模塊負責把數字下變頻數據通過CPRI幀發送給SCAN25100,接收模塊則把接收的CPRI幀提取出數字上變頻需要的數據。只有當啟動模塊完成后。輸出1個控制信號,數字中頻和CPRI之間才能互相傳遞數據。

?

?

?

3.2.1 發送模塊

按照CPRI基本幀和超幀結構,把DDC(數字下變頻)的IQ數據信號與相應的控制信號成幀后發送給SCAN25100,SCAN25100再進行8 B/10 B編碼,從光模塊發送出去。如圖7所示,TXMGR模塊產生IQ數據和控制數據的使能信號;TXCTRL模塊則對CPRI超幀的控制時隙進行狀態轉換,產生不同的控制信號,從而從FIFO中選擇讀出不同的控制信號;TXDDR模塊則是把數據通過時鐘雙邊沿進行發送。

?

?

?

3.2.2 接收模塊

將從SCAN25100接收到的數據進行同步頭(K28.5)檢測,進行CPRI解幀工作,把控制信號和IQ數據信號分解出來,IQ數據信號送到DUC(數字上變頻)。如圖8所示,RXDDR模塊則是通過時鐘雙邊沿接收數據;RxMGR模塊通過檢測幀頭產生IQ數據和控制數據的使能信號;RXCTRL模塊則對CPRI超幀的控制時隙進行狀態轉換,產生不同的控制信號,從而把接收到不同的控制信號寫入FIFO,提供給其他模塊。

?

?

?

3.2.3 CPRI啟動過程模塊

CPRI規范中的啟動過程,此過程是相當重要的,需要軟件和硬件共同完成。協商確定物理層的協議、慢速通道(HDLC)和快速通道(以太網)的傳輸速率,完成REC和RE之間的鏈路建立,從而進行正常的通信過程。在設計過程中,理清各個狀態的作用,利用狀態機實現啟動過程,整個流程如圖9所示。

?

?

?

4 實際測試結果

4.1 自環測試

在實驗室常溫環境下進行實際測試,采用Chips-cope抓取發送和接收的數據進行比較的方法。也就是說,產生一段測試數據,按CPRI幀格式發送給sCAN25100,通過光模塊自環回來,如圖3所示,然后用Chipscope抓取接收回來的數據,與發送的數據進行對比,確認鏈路是正常通信。

?

?

?

經過反復測試,該系統已經能正常穩定通信,如圖10所示。發送數據(Txdata)幀頭為OxBC50,發送時刻為2172,隨后的發送數據的高8位和低8位分別以2累加。接收數據(RxData)在2193時刻接收到幀頭OXBC50,隨后接收到的數據也是高8位和低8位分別以2累加,而且跟發送的數據是一樣的。

4.2 聯合測試

CPRI模塊的成解幀都是在FPGA內部完成的,而數字中頻模塊(DDC,DUC)也全部在FPGA里面完成設計,如圖6所示。兩部分的接口顯得非常簡單,只需要把兩部分代碼整合成一個工程就行。同樣,在實驗室常溫環境下進行測試,整個系統能正常穩定的工作。

5 結 語

CPRI是規范基站內部REC和RE之間的接口標準協議。該設計把CPRI的兩層協議分開設計實現,FPGA實現CPRI鏈路層,設計靈活。芯片SCAN25100實現物理層,由于芯片具備自動同步及準確校準時延等功能,方便后續設計分布式遠程射頻基站系統。通過對電路板的實際測試,調整電路設計及PCB部分布線設計,不斷地調整優化設計,CPRI模塊正常穩定工作,該模塊已經和其他模塊(DDC,DUC等)通過了聯合測試。

電子發燒友App

電子發燒友App

評論