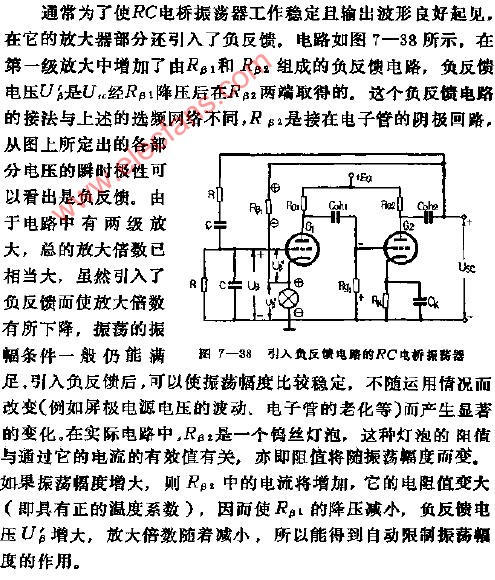

文氏(Wien)網絡自1891年由物理學家Max Wien推導出以來,已被用于許多振蕩器設計中,其中最著名的是惠普200振蕩器。讓這個正弦波振蕩器的設計與當時的大部分設計不同的關鍵,是在負反饋分壓器中使用白熾燈來穩定恒定振幅電平所需的增益,以及在寬頻率范圍內穩定的振蕩器運行。這是Fred Terman教授給Bill Hewlett(惠普的兩個創始人之一)的斯坦福大學碩士論文的建議。Bill Hewlett的音頻振蕩器變得相當有名,是日后與Dave Packard創立的惠普公司的第一批產品。在Bill Hewlett推出其文氏電橋振蕩器之前,大多數音頻源都是基于LC振蕩器的。

通用無線電公司(GR)自1920年代后期就開始生產音頻振蕩器,最初是403型,后來發展到1304型。GR音頻振蕩器由兩個LC調諧振蕩器組成,一個振蕩器是固定頻率,另一個是可調的。兩個振蕩器的輸出混合在一起。不在振蕩器指定范圍內的頻率被濾除,所選的頻帶被放大,且振幅被調平并被控制饋送到振蕩器的輸出端。這種制造音頻信號源的方法昂貴且復雜。由于LC調諧振蕩器會漂移,因此難以保證頻率穩定性。較低音頻頻率下的頻率穩定性成為LC調諧音頻振蕩器永無止境的問題。諧波失真是另一個重要問題。

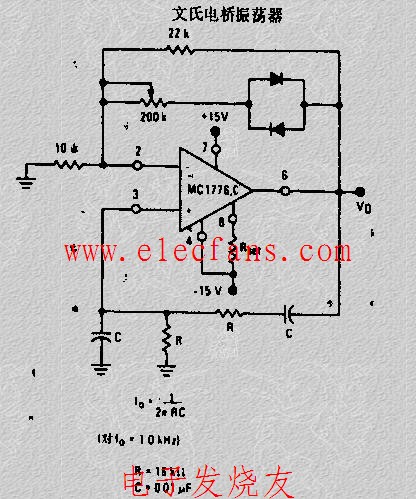

固定或單頻文氏電橋振蕩器不難設計和建構,因為在文氏電橋網絡中可以選配RC組件以實現所需的振蕩頻率。

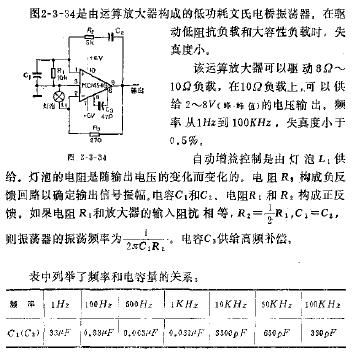

使用Bill Hewlett引入的燈泡發熱方案可以實現幅值控制穩定。這種文氏電橋振蕩器可以實現非常低的失真,具有良好的振幅和頻率穩定性。

由于文氏電橋網絡的電阻臂或電容臂中需要一對匹配元件,所以變頻文氏電橋振蕩器的設計和建構更加困難。這可通過一個雙可變跟蹤電容器或開關電容值、雙可變跟蹤電阻器、開關電阻器以及邏輯選擇電阻器(數字電位器)以改變頻率的方法來實現。

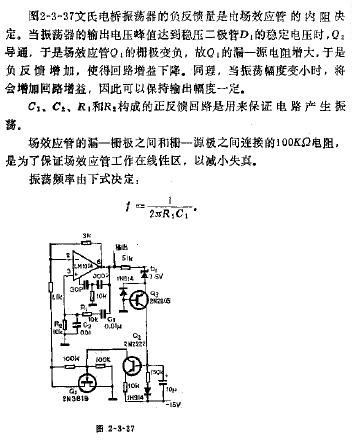

電壓調諧的文氏電橋振蕩器并不常見,它們可能對設計和建構帶來挑戰。基于變容二極管(壓變電容器)的文氏電橋壓控振蕩器設計和建構一直存在。另一種調整文氏網絡的方法是使用一對匹配的JFET。

Linear Systems推出的雙匹配P溝道JFET激發了在文氏網絡中使用該匹配器件作為跟蹤壓控電阻的設想。1967年,Oliver A. Fick和原子能委員會(Atomic Energy Commission)為此申請了專利。專利中有這一概念和設想的描述與圖示,但與大多數專利一樣,如何使這一設想實際發揮效能的更具體的細節模糊不清,其詳盡程度不足以在現實中實現足夠好的設計。雖然多年鼓搗測試儀器,從其服務手冊中搜集了大量信息,并在網上查找JFET調諧的文氏電橋振蕩器的例子,仍沒有發現可行的設計。這一設想激發了設計和構建滿足功能要求的JFET電壓調諧文氏電橋振蕩器的好奇心。

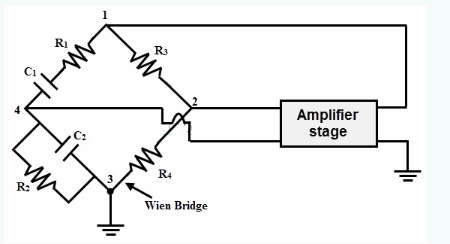

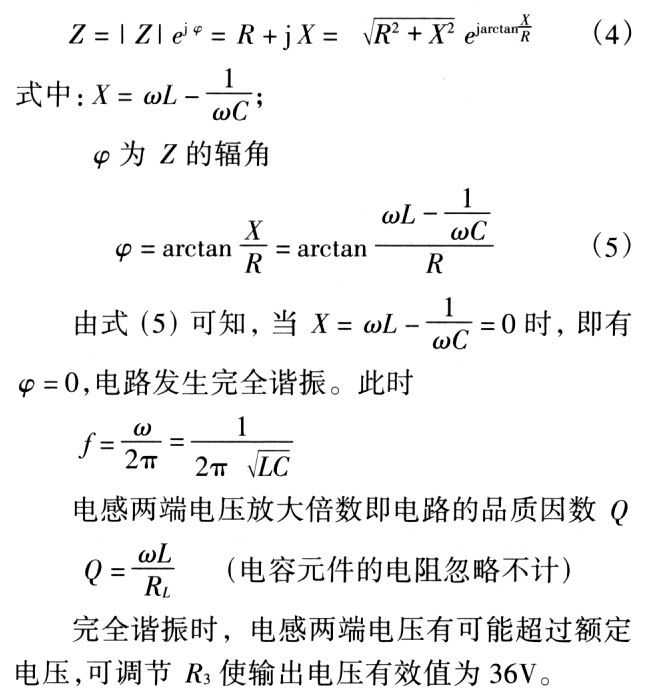

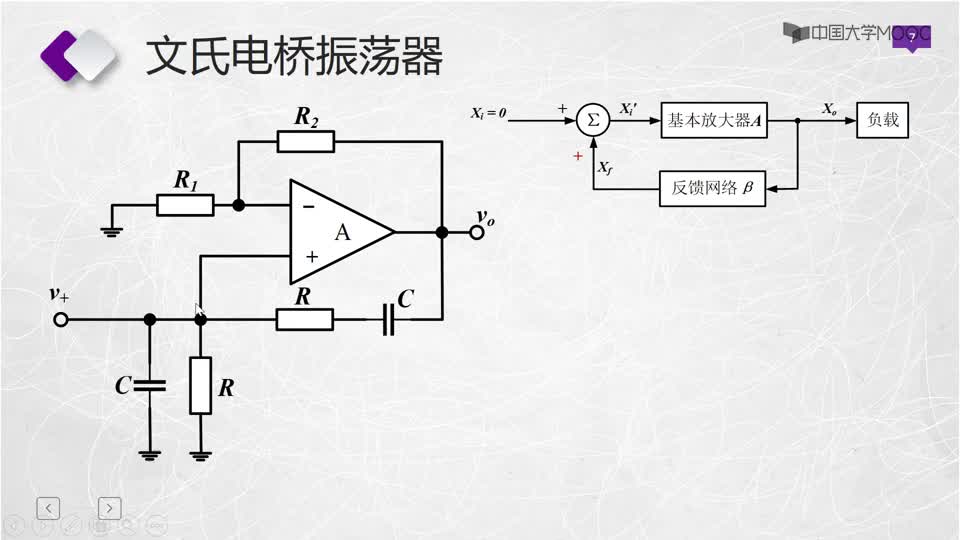

文氏電橋本質上是一個串并聯RC網絡,當串聯和并聯RC網絡達到平衡時,相移為零。在零相移時,該網絡本質上變成一個電阻分壓器,可用于將正反饋送入放大器,以產生特定頻率的振蕩。

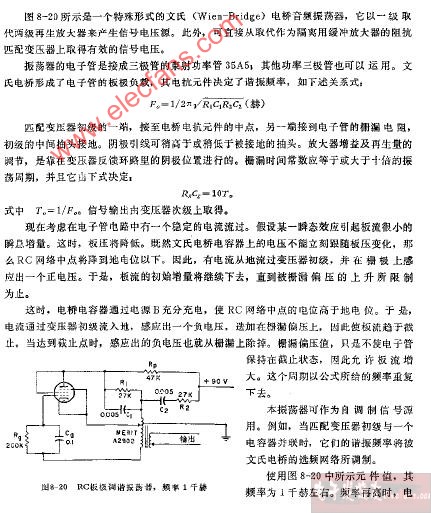

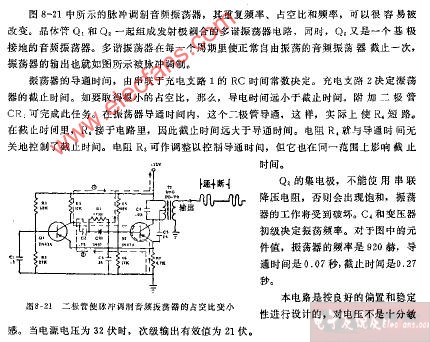

圖1:使用惠普3577B網絡分析儀的文氏網絡分析儀繪圖示例。

該文氏網絡的電容值為1000pF、電阻為301Ω。由計算得出發生零相位的頻率為512kHz,網絡分析儀顯示接近513kHz。文氏網絡損耗約9.5dB或3倍衰減。這是當文氏網絡作為正反饋插入到振蕩器中時,為了產生振蕩,放大器或類似增益器件需要補償的能量損耗量。增益器件會增加振蕩幅度,直到飽和為止。增加一個由參考電壓控制的可變增益負反饋環路,通過文氏網絡來平整和平衡正反饋的量值,可以得到穩定的振蕩器輸出振幅和振蕩頻率。

圖2:降低文氏網絡串聯臂的電阻或R值,會導致網絡分析儀顯示器在平衡狀態下幅度略微增加,頻率略微上移。

當文氏網絡用作振蕩器時,稍微增加了其正反饋量。為保持振蕩器的恒定電平輸出,負反饋環路需要調整并補償這些動態文氏網絡調諧組件的變化。

這是在文氏電橋振蕩器中使用JFET作為壓控運行元件時需要考慮的一個參數示例。

用作壓控電阻時,JFET具有與三極真空管類似的基本平方定律非線性傳輸特性。因為JFET的漏極和源極會增加信號偏移水平,從而導致通道長度調制(通道電阻調制),JFET的這一“個性”就更得以彰顯。圖3中貫通被測JFET的三角波兩邊的曲率顯示了漏-源阻抗的這些小變化。

雙LSJ689的一半配置為雙電阻分壓器中的一個電阻,由底部的10V峰-峰、500kHz三角波曲線驅動;柵-源極偏置電壓約為JFET漏-源極接近最大源 - 漏極電阻時偏置電壓的30%。

圖3:頂部三角波曲線(曾為直線)邊緣呈現了JFET的平方律特性。

大多數JFET的漏極至源極通常是對稱的。通過在柵極與漏極之間增加分壓器,將柵極連接到分壓器中心,該分壓器就能有效地向JFET的柵極施加校正反饋。

圖4:由信道長度調制引起的一些非線性可以得到校正。

將來自JFET的漏極到源極之間的電阻分壓器的反饋添加到柵極有助于FET線性化。

將分壓器驅動增加到15V峰-峰值電壓,以說明被測JFET上漏-源極電阻線性度的改善。

通過降低漏-源極間的信號電平,可進一步降低由漏-源極間壓降引起的柵極調制導致的JFET失真。這有效減小了溝道長度調制效應,使JFET的漏-源極之間的阻抗更線性。

圖5:頂部跡線,被測JFET的輸出三角波;底部跡線,輸入到JFET測試分壓器的三角波。

JFET不是理想電阻器

JFET不是理想電阻器,盡管有局限,LSJ689中的兩個匹配JFET仍足以用作文氏電橋調諧元件。作為P溝道JFET的LSJ689具有正向電壓增加JFET漏-源電阻的優點。與需要負向電壓增加JFET漏-源極電阻的N溝道JFET相比,前者電壓控制更加容易。

柵-源極電壓為零時,LSJ689的典型“導通”電阻約為120Ω。數據手冊規定柵-源極“OFF”(漏-源極電阻達到該JFET能夠獲得的最大值)電壓在1.5至5V之間。該規范會影響給定柵-源極電壓下漏-源電阻的量值,從而直接影響文氏網絡的調諧頻率和調諧范圍。 JFET對漏-源電阻之間的差異將影響文氏電橋的調諧頻率和幅度,如網絡分析儀圖所示。在1MHz、漏-源極電壓為15V時,LSJ689具有8pF的低漏-源極電容。鑒于LSJ689的這些固有特征,我們來嘗試制作一款250kHz至1MHz、電壓調諧的文氏電橋振蕩器。

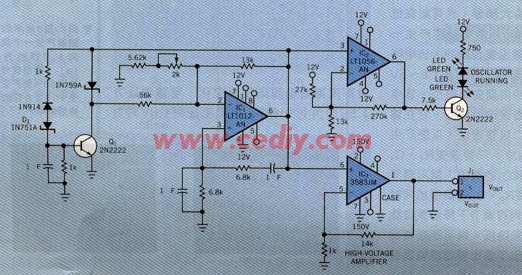

文氏電橋振蕩器中用作增益元件的放大器是非常基本的三極管差分放大器,帶有互補的發射極跟隨器輸出部分。設計并不復雜,在1MHz振蕩器中具有足夠的帶寬來工作,具有低阻抗的正和負反饋回路,并且仍具有一定的負載驅動能力。開環增益在14左右,便于反饋回路閉合(振蕩所需的增益約為9.5dB或x3),具有合理的失真性能和可接受的DC穩定性。

K489A-K489B是在輸入端使用的LSK489匹配的N通道對。該差分對的尾電流由J511電流源二極管設定為約4.5mA,并在差分對的兩個JFET間分流。同相輸入JFET K489A具有一個1kΩ的負載電阻R9和一個二極管D1。1kΩ電阻將增益設置為約等于2。二極管在R9兩端增加了一個二極管壓降,幫助補償和抵消連接到它的共發射極放大器導致的溫度影響。反相輸入JFET(K489B)作為源極跟隨器,增加了該放大器輸入負反饋路徑的阻抗。

Q2是共發射極放大器(CE),其直流偏置是通過漏極電阻R9和D1兩端的壓降實現的,增益由直流偏移調整器R11、R12、Re‘’、集電極電阻R13和發射極跟隨器輸出部分所需的能量設置。可變電阻R11用于調整放大器的直流偏移,通過調整進入R13的集電極電流實現。R13上產生的壓降被設定為在放大器的輸出端達到接近零伏時的電壓。該CE放大器的工作電流為11mA,支持所需放大器的帶寬以及發射極跟隨器輸出部分的驅動需要足夠的電流。由于使用本地反饋將該放大器CE部分的增益設置為約等于7,利用Q2的固有集電極-基極電容保證了放大器穩定性。

三個二極管D3、D4、D5產生約1.8V壓降,以偏置用作輸出級的NPN和PNP發射極跟隨器。發射極跟隨器上的基極電阻R14、R15是保證良好的振蕩穩定性必需的;發射極電阻R16、R17需要在溫度范圍內保持偏置穩定性。輸出部分偏置設置為12mA,允許在驅動低阻抗文氏網絡正反饋環路和光敏電阻調制的負反饋環路的同時,仍有一些電流可用于驅動負載。

電壓調諧文氏電橋網絡包括用作壓控電阻器對的LSJ689雙P溝道JFET。漏-柵極反饋電阻R3、R6有助于JFET的有效電阻曲線線性化;R2、R5則構成J689A和J689B的柵極分壓器。JFET上并聯的R4、R7在柵極電壓變化時將其可變電阻范圍限制在約120Ω到650Ω的范圍,同時也有助于JFET的電阻曲線線性化。 C3對JFET調諧電壓進行隔離,以遠離放大器的同相輸入端。 6.8V齊納二極管限制了可施加到JFET柵極的電壓,從而有效限制了這種電壓調諧的文氏電橋振蕩器的可變電阻范圍和調諧頻率范圍。

R1限制了齊納二極管D2的電流,C7和R1對進出振蕩器的一些高頻控制電壓進行濾波,C1和C2構成了文氏網絡的剩余部分,振蕩器頻率隨調諧電壓的增加而降低。

在本文末尾的示意圖中,當電壓控制(VC)輸入為0V時,文氏網絡振蕩頻率約為1MHz,當VC輸入為7V時,振蕩頻率下降到約250kHz,也即每伏下降110kHz。由于JFET固有的非線性,每伏對應的調諧頻率并非線性。

圖6:頂部跡線是0V到10V,一個2s的斜坡驅動VC輸入;底部跡線是振蕩器的輸出,從1MHz開始,停止在250kHz;跡線包絡說明在其調諧頻率范圍內具有均勻的振蕩器電平輸出。

為了控制和穩定振蕩器的輸出電平,D6、D7、R21構成Q4的1.2V基準電壓,從而在發射極電阻R22上產生約0.6V電壓,生成2mA的電流源。

這個2mA的電流被施加到D11,D11中注入1.8mA將使R19的電阻降低到約100Ω。在R19為100Ω、固定負反饋電阻R18為619Ω的條件下,放大器的閉環增益增加到約等于7。這一量值的放大器增益加之相關部件的固有噪聲就可以啟動振蕩器。一旦振蕩器的輸出電平足夠高以驅動峰值檢測器網絡R23、D8、C4,分壓器R24、R26就設置基極驅動量值來正向偏置Q5的基極-發射極結。分壓器R24、R26還設置了振蕩器的輸出電平。一旦Q5有足夠的基極驅動來克服其基極-發射極電壓,那么它還可以用作振蕩器電平控制的參考電壓。Q5開始導通,電流開始從集電極流向發射極,從而減小驅動D11的電流。減小對D11的驅動會增加R19的阻值,改變R18的分壓比,降低放大器增益,穩定并平衡振蕩器的輸出。振蕩器電平控制環路的穩定性由C4、R24、R26和固有的LED光輸出到光敏電阻的阻值變化-反應時間(轉化為光敏電阻模塊D11-R19)所決定。

圖7:振蕩器輸出的諧波分量在1MHz時驅動500Ω負載。

電源去耦網絡

L1、L2、R28、R29、C5、C6組成電源去耦網絡。電感的阻抗隨頻率的增加而增加,限制了可以進入或離開振蕩器的較高頻能量的量值。R28、R29消除了網絡的潛在自諧振。旁路電容需要一些阻抗來抑制,否則將成為不想要的循環電流發生器,從而導致意外的問題。

振蕩器+/-15V電源直接連接到22μF旁路電容。

*圖8:頂部跡線:+15V電源、Tek P6021電流探頭和Tek 7A14(@ 5mA /格),使電源產生脈沖電流,驅動振蕩器和500Ω負載,可見。中間跡線:+ 15V電源、Tek P6046差分探頭(@10mV/格),顯示+15V電源的電壓紋波;用電壓探頭實際看不到電流脈沖。底部跡線:振蕩器輸出至500Ω負載。振蕩器+/- 15V電源連接到150μH電感、10Ω電阻和22μF旁路電容。

圖9:頂部跡線:+15V電源、Tek P6021電流探頭和Tek 7A14(@ 5mA /格);驅動振蕩器和500Ω負載的脈沖電流由150μH電感、10Ω電阻和22uF旁路電容控制。中間跡線:+15V電源、Tek P6046差分探頭(@10mV/格)、在+15V電源上顯示電壓紋波;有或沒有150μH電感和10Ω電阻,看起來差不多。底部跡線:振蕩器輸出到500Ω負載。

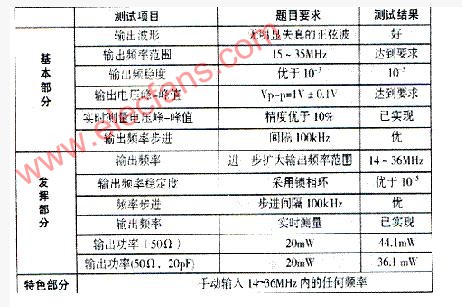

JFET電壓調諧文氏電橋振蕩器的測量規范:

頻率范圍:250kHz至1MHz。

調諧靈敏度:110kHz/V

諧波:最大-30dBc。

輸出電平:1VRMS、+/- 0.3dB饋送至150Ω負載。

該JFET電壓調諧文氏電橋振蕩器說明如何進行設計權衡來實現可工作的振蕩器。調諧頻率范圍受限于匹配的P溝道JFET對的線性調諧范圍。將頻率調諧范圍擴大到本范例之外會導致文氏網絡的有效電阻值過度失配,使文氏網絡失衡。考慮到JFET 文氏網絡的這些限制,調諧靈敏度最終會達到110kHz/V左右。對于1MHz中心頻率、30kHz步進來說,該VCO的階躍響應或調諧速率被幅度控制環路限制為1ms。在1MHz、振蕩器輸出負載為500Ω的情況下,諧波比最差情況下的基本調諧頻率(-dBc)低-30dB。這是由文氏電橋失配、放大器性能、振蕩器輸出電平驅動500Ω負載等情況決定的。這種FET調諧的VCO的電性能與使用變容二極管的LC電壓調諧振蕩器類似。

文氏網絡是橋網絡的實例,它是模擬電子學的基本構建模塊之一。橋網絡演變而來的還包括由四個電阻組成的惠斯登電橋,然后是進一步的差分放大器。最基本的差分放大器是由兩個負載電阻和兩個有源器件(FET、MOSFET、雙極型晶體管、真空管、微型抗震電子管等)組成。利用四元網絡在兩邊實現平衡和對稱,這是一個非常有效的設計理念。這種平衡和對稱的概念體現在模擬電路設計的許多方面,類似于自然系統之于人類行為。

幅度控制系統環路是平衡的另一種演變。它包括一個參考,該參考與幅度值進行比較。比較結果產生一個差值或誤差信號,使用增益控制元件改變放大器增益就可以控制文氏電橋振蕩器的輸出電平。實施放大器增益校正(校正事件時間)和決定需要施加多少幅度校正,增加了幅度控制環的復雜性。如果不以適當的時序和量值進行校正,控制系統會變得不穩定。

JFET文氏電橋振蕩器的設計和構建也使旁路電容一些“隱藏”的影響顯露出來。旁路電容可以是有效的瞬時儲能器件,也可以成為電壓-電流轉換器。電流探頭有助于說明旁路電容對電流轉換的影響。由于旁路電容會產生有效低阻抗電壓源,因此使用電壓探頭不易揭示此現象。

?

圖10:電流探頭有助于說明旁路電容對電流轉換的影響。

增加電感作為附加的瞬時能量存儲元件(阻抗隨頻率的增加而增加),降低了通過電源“逃離”該電路的高頻。與電感串聯的電阻防止該網絡變成諧振回路。

電子發燒友App

電子發燒友App

評論