歷經(jīng)四年的開(kāi)發(fā)和一年的試用版本測(cè)試,賽靈思可編程顛覆之作 Vivado 設(shè)計(jì)套件終于震撼登場(chǎng),并通過(guò)其早期試用計(jì)劃開(kāi)始向客戶(hù)隆重推出。新的工具套件面向未來(lái)十年 “All-Programmable”器件而精心打造, 致力于加速其設(shè)計(jì)生產(chǎn)力。

賽靈思市場(chǎng)營(yíng)銷(xiāo)與公司戰(zhàn)略高級(jí)副總裁Steve Glaser表示:“在過(guò)去的幾年中,賽靈思把??半導(dǎo)體技術(shù)的創(chuàng)新推向了一個(gè)新的高度,并釋放了可編程器件全面的系統(tǒng)級(jí)能力。隨著賽靈思在獲獎(jiǎng)的Zynq?-7000 EPP(可 擴(kuò)展式處理平臺(tái))器件、革命性的3D Virtex?-7堆疊硅片互聯(lián)(SSI)的技術(shù)器件上的部署, 除了我們?cè)?a target="_blank">FPGA技術(shù)上的不斷創(chuàng)新之外, ,我們正開(kāi)啟著一個(gè)令人興奮的新時(shí)代——一個(gè)“All Programmable”器件的時(shí)代。”

“All Programmable”器件,將使設(shè)計(jì)團(tuán)隊(duì)不僅能夠?yàn)樗麄兊脑O(shè)計(jì)編程定制邏輯,而且也可以基于ARM?和賽靈思處理子系統(tǒng)、算法和I / O進(jìn)行編程。總之,這是一個(gè)全面的系統(tǒng)級(jí)的器件。Steve Glaser說(shuō)“未來(lái)“All Programmable”器件要比可編程邏輯設(shè)計(jì)更多。他們將是可編程的系統(tǒng)集成,投入的芯片越來(lái)越少,而集成的系統(tǒng)功能卻越來(lái)越多。”

Steve Glaser還表示,在利用“All Programmable”器件創(chuàng)建系統(tǒng)的時(shí)候,設(shè)計(jì)者所面臨的是一套全新的集成和實(shí)現(xiàn)設(shè)計(jì)生產(chǎn)力的瓶頸問(wèn)題。一方面從集成的角度講,其中包括集成算法C和寄存器傳輸級(jí)(RTL)的IP;混合了DSP、嵌入式、連接和邏輯域;驗(yàn)證模塊和“系統(tǒng)”,以及設(shè)計(jì)和IP的重用等。實(shí)現(xiàn)的瓶頸包括芯片規(guī)劃和分層;多領(lǐng)域和大量的物理優(yōu)化;多元的“設(shè)計(jì)”與“時(shí)序”收斂;和后期的ECO和設(shè)計(jì)變更的連鎖效應(yīng)。

正是為了解決集成和實(shí)現(xiàn)的瓶頸,使用戶(hù)能夠充分利用這些“All Programmable”器件的系統(tǒng)集成能力,賽靈思打造了全新Vivado設(shè)計(jì)套件。

在Vivado 設(shè)計(jì)套件這一以系統(tǒng)為中心的工具套件的開(kāi)發(fā)過(guò)程中,賽靈思以業(yè)界標(biāo)準(zhǔn)為標(biāo)桿并采用了先進(jìn)的 EDA 技術(shù)與方法。為此,無(wú)論是需要高度自動(dòng)化按鍵式流程的客戶(hù),還是需要實(shí)際操作性極強(qiáng)的可修改流程的客戶(hù),他們現(xiàn)在能夠比以往更快更高效地進(jìn)行設(shè)計(jì)(甚至包括賽靈思最大型的 FPGA 設(shè)計(jì)),同時(shí)還是在一個(gè)熟悉而直觀的先進(jìn)的 EDA 環(huán)境下工作。

賽靈思開(kāi)發(fā) Vivado 設(shè)計(jì)套件的目的是為客戶(hù)提供一種具有完整系統(tǒng)可編程功能的新型工具套件,該套件遠(yuǎn)遠(yuǎn)超越了賽靈思為時(shí)甚久的旗艦型 ISE 設(shè)計(jì)套件。為幫助客戶(hù)順利過(guò)渡到Vivado 設(shè)計(jì)套件的使用,賽靈思將繼續(xù)堅(jiān)定地為采用 7 系列及更早期的賽靈思 FPGA 技術(shù)的客戶(hù)提供 ISE 支持。今后 Vivado 設(shè)計(jì)套件將成為賽靈思的旗艦設(shè)計(jì)環(huán)境,支持所有 7 系列器件及賽靈思未來(lái)器件。

賽靈思公司設(shè)計(jì)方法市場(chǎng)營(yíng)銷(xiāo)高級(jí)總監(jiān) Tom Feist 預(yù)計(jì),一旦客戶(hù)啟用 Vivado 設(shè)計(jì)套件,就會(huì)立即體會(huì)到其相對(duì)于 ISE 的優(yōu)勢(shì)。

Feist說(shuō):“與同類(lèi)競(jìng)爭(zhēng)工具相比,Vivado 設(shè)計(jì)套件的運(yùn)行時(shí)間可縮短高達(dá) 4 倍,能夠顯著提升用戶(hù)的設(shè)計(jì)生產(chǎn)力。同時(shí)該設(shè)計(jì)套件純熟地運(yùn)用了多種業(yè)界標(biāo)準(zhǔn),諸如 System Verilog、SDC(Synopsys 設(shè)計(jì)約束)、C/C++/System C、ARM AMBA AXI-4互聯(lián)、互動(dòng) TCL(工具命令語(yǔ)言)腳本。Vivado 設(shè)計(jì)套件的其它突出優(yōu)勢(shì)包括為 Vivado 的眾多報(bào)告和設(shè)計(jì)視圖提供全面的交叉探測(cè)功能、預(yù)計(jì)將于 2012 年推出的高級(jí)圖形化 IP 集成功能、首款得到 FPGA 廠商全面支持的商用高層次綜合技術(shù)(C++ 到 HDL綜合)。

一個(gè)面向新一代可編程設(shè)計(jì)的設(shè)計(jì)工具

賽靈思早在 1997 年就推出了 ISE 設(shè)計(jì)套件。ISE套件采用了當(dāng)時(shí)非常具有創(chuàng)新性的基于時(shí)序的布局布線引擎,這是1995 年 4 月賽靈思收購(gòu) NeoCAD 獲得的。在其后 15 年的時(shí)間里,隨著 FPGA 能夠執(zhí)行日趨復(fù)雜的功能,賽靈思為 ISE 套件增添了許多新技術(shù),包括多語(yǔ)言綜合與仿真、IP 集成以及眾多編輯和測(cè)試實(shí)用功能,努力不斷從各個(gè)方面改進(jìn) ISE 設(shè)計(jì)套件。Feist 表示,賽靈思通過(guò)借鑒 ISE 設(shè)計(jì)套件的所有經(jīng)驗(yàn)、注意事項(xiàng)和關(guān)鍵技術(shù),并充分利用最新 EDA 算法、工具和技術(shù),才打造出了這一顛覆性的全新 Vivado 設(shè)計(jì)套件。

Feist 表示:“Vivado 設(shè)計(jì)套件將顯著提升當(dāng)今設(shè)計(jì)的生產(chǎn)力,且能夠輕松實(shí)現(xiàn)升級(jí)擴(kuò)展,應(yīng)對(duì)20nm 芯片及更小工藝技術(shù)所帶來(lái)的容量和設(shè)計(jì)復(fù)雜性挑戰(zhàn)。在過(guò)去 15 年時(shí)間里,EDA 技術(shù)取得了長(zhǎng)足的發(fā)展。我們是從頭開(kāi)始開(kāi)發(fā)這套工具的,所以我們能夠在套件中采用最先進(jìn)的 EDA 技術(shù)和標(biāo)準(zhǔn),讓其具有很強(qiáng)的前瞻性。”

確定性的設(shè)計(jì)收斂

任何 FPGA 廠商的集成設(shè)計(jì)套件的核心都是物理設(shè)計(jì)流程,包括綜合, 布局規(guī)劃、布局、布線、功耗和時(shí)序分析、優(yōu)化和ECO。 有了Vivado,賽靈思打造了一個(gè)最先進(jìn)的設(shè)計(jì)實(shí)現(xiàn)流程,可以讓客戶(hù)更快地達(dá)到設(shè)計(jì)收斂的目標(biāo)。

可擴(kuò)展的數(shù)據(jù)模型架構(gòu)

為減少迭代次數(shù)和總體設(shè)計(jì)時(shí)間,并提高整體生產(chǎn)力,賽靈思用一個(gè)單一的、共享的、可擴(kuò)展的數(shù)據(jù)模型建立其設(shè)計(jì)實(shí)現(xiàn)流程,這種框架也常見(jiàn)于當(dāng)今最先進(jìn)的 ASIC 設(shè)計(jì)環(huán)境。Feist 說(shuō):“這種共享、可擴(kuò)展的數(shù)據(jù)模型可讓流程中的綜合、仿真、布局規(guī)劃、布局布線等所有步驟在內(nèi)存數(shù)據(jù)模型上運(yùn)行,故在流程中的每一步都可以進(jìn)行調(diào)試和分析,這樣用戶(hù)就可在設(shè)計(jì)流程中盡早掌握關(guān)鍵設(shè)計(jì)指標(biāo)的情況,比如時(shí)序、功耗、資源利用和布線擁塞等。而且這些指標(biāo)的估測(cè)將在實(shí)現(xiàn)過(guò)程中隨著設(shè)計(jì)流程的推進(jìn)而更趨于精確。”

具體來(lái)說(shuō),這種統(tǒng)一的數(shù)據(jù)模型使賽靈思能夠?qū)⑵湫滦投嗑S分析布局布線引擎與套件的 RTL 綜合引擎、新型多語(yǔ)言仿真引擎以及 IP 集成器 (IP Integrator)、引腳編輯器 (Pin Editor)、布局規(guī)劃器 (Floor Planner)、芯片編輯器 (Chip Editor) 等功能緊密集成在一起。此外,該數(shù)據(jù)模型使賽靈思能夠?yàn)樵摴ぞ咛准鋫淙娴慕徊嫣綔y(cè)功能,以便用戶(hù)跟蹤并交叉探測(cè)原理圖、時(shí)序報(bào)告、邏輯單元或其它視圖,直至 HDL 代碼中的給定問(wèn)題。

Feist說(shuō):“用戶(hù)現(xiàn)在可以對(duì)設(shè)計(jì)流程中的每一步進(jìn)行分析,而且環(huán)環(huán)相扣。在綜合后的流程中,我們還提供時(shí)序、功耗、噪聲和資源利用分析功能。所以如果很早就發(fā)現(xiàn)時(shí)序或功耗不符合要求,我可以通過(guò)短時(shí)迭代,前瞻性地解決問(wèn)題,而不必等到布局布線完成后多次執(zhí)行長(zhǎng)時(shí)間迭代來(lái)解決。”

Feist 指出,這種可擴(kuò)展數(shù)據(jù)模型提供的緊密集成功能還增強(qiáng)了按鍵式流程的效果,從而可滿足用戶(hù)對(duì)工具實(shí)現(xiàn)最大自動(dòng)化,完成大部分工作的期望。Feist 表示,這種模型還能夠滿足客戶(hù)對(duì)更高級(jí)的控制、更深入的分析以及掌控每個(gè)設(shè)計(jì)步驟進(jìn)程的需要。

芯片規(guī)劃層次化,快速綜合

Feist說(shuō), Vivado為用戶(hù)提供了設(shè)計(jì)分區(qū)的功能, 可以分別處理綜合、執(zhí)行、驗(yàn)證的設(shè)計(jì), 使其可以在執(zhí)行大型項(xiàng)目時(shí),可以成立不同的團(tuán)隊(duì)分頭設(shè)計(jì)。 同時(shí),新的設(shè)計(jì)保存功能可以實(shí)現(xiàn)時(shí)序結(jié)果的復(fù)用, 并且可以實(shí)現(xiàn)設(shè)計(jì)的部分可重配置。

Vivado還包括一個(gè)全新的綜合引擎,旨在處理數(shù)以百萬(wàn)計(jì)的邏輯單元。新的綜合引擎的關(guān)鍵是對(duì)System Verilog的強(qiáng)大支持。“Vivado的綜合引擎對(duì)System Veriog語(yǔ)言可綜合子集的支持, 比市場(chǎng)上任何其他工具都更好” Feist 說(shuō)。 它的綜合速度是賽靈思ISE Design Suite綜合工具XST的三倍,并支持“快速”模式,使得設(shè)計(jì)師迅速把握設(shè)計(jì)的面積和規(guī)模。 另外,也讓他們調(diào)試問(wèn)題的速度比之前采用RTL或門(mén)級(jí)原理圖快15倍。隨著越來(lái)越多的ASIC設(shè)計(jì)者轉(zhuǎn)向可編程平臺(tái),賽靈思還在整個(gè)Vivado設(shè)計(jì)流程中提升了了Synopsys 設(shè)計(jì)約束 (SDC)。標(biāo)準(zhǔn)的使用開(kāi)啟了一個(gè)新的自動(dòng)化水平, 客戶(hù)現(xiàn)在可以訪問(wèn)先進(jìn)的EDA工具產(chǎn)生約束、檢查跨時(shí)鐘域、形式驗(yàn)證, 甚至是利用像Synopsys PrimeTime那樣的工具進(jìn)行靜態(tài)時(shí)序的分析。

賽靈思vivado設(shè)計(jì)套件專(zhuān)題:http://www.nxhydt.com/topic/tech/vivado/

多維度分析布局器

Feist 解釋說(shuō),上一代 FPGA 設(shè)計(jì)套件采用單維基于時(shí)序的布局布線引擎,通過(guò)模擬退火算法隨機(jī)確定工具應(yīng)在什么地方布置邏輯單元。使用這類(lèi)工具時(shí),用戶(hù)先輸入時(shí)序,模擬退火算法根據(jù)時(shí)序先從隨機(jī)初始布局種子開(kāi)始,然后在本地移動(dòng)單元,“盡量”與時(shí)序要求吻合。Feist 說(shuō):“在當(dāng)時(shí)這種方法是可行的,因?yàn)樵O(shè)計(jì)規(guī)模非常小,邏輯單元是造成延遲的主要原因。但今天隨著設(shè)計(jì)的日趨復(fù)雜化和芯片工藝的進(jìn)步,互聯(lián)和設(shè)計(jì)擁塞一躍成為延遲的主因。采用模擬退火算法的布局布線引擎對(duì)低于 100 萬(wàn)門(mén)的 FPGA 來(lái)說(shuō)是完全可以勝任的,但對(duì)超過(guò)這個(gè)水平的設(shè)計(jì),引擎便不堪重負(fù)。不僅僅有擁塞的原因,隨著設(shè)計(jì)的規(guī)模超過(guò)100萬(wàn)門(mén),設(shè)計(jì)的結(jié)果也開(kāi)始變得更加不可預(yù)測(cè)。”

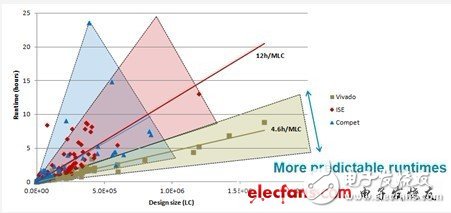

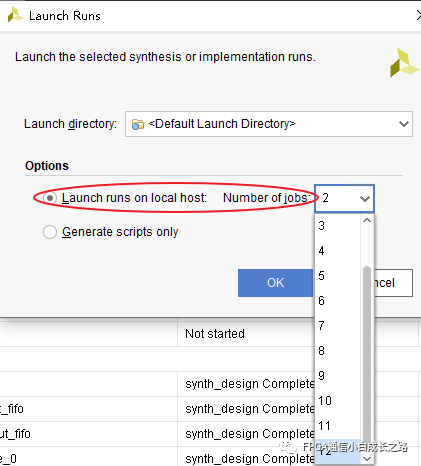

著眼于未來(lái),賽靈思為 Vivado 設(shè)計(jì)套件開(kāi)發(fā)了新型多維分析布局引擎,其可與當(dāng)代價(jià)值百萬(wàn)美元的 ASIC布局布線工具中所采用的引擎相媲美。該新型引擎通過(guò)分析可以找到從根本上能夠最小化設(shè)計(jì)三維(時(shí)序、擁塞和走線長(zhǎng)度)的解決方案。Feist 表示:“Vivado設(shè)計(jì)套件的算法從全局進(jìn)行優(yōu)化,同時(shí)實(shí)現(xiàn)了最佳時(shí)序、擁塞和走線長(zhǎng)度,它對(duì)整個(gè)設(shè)計(jì)進(jìn)行通盤(pán)考慮,不像模擬退火算法只著眼于局部調(diào)整。這樣該工具能夠迅速、決定性地完成上千萬(wàn)門(mén)的布局布線,同時(shí)保持始終如一的高結(jié)果質(zhì)量(見(jiàn)圖 1)。由于它能夠同時(shí)處理三大要素,也意味著可以減少重復(fù)運(yùn)行流程的次數(shù)。”

圖1:與其它 FPGA 工具相比,Vivado 設(shè)計(jì)套件能夠以更快的速度、更優(yōu)異的質(zhì)量完成各種規(guī)模的設(shè)計(jì)

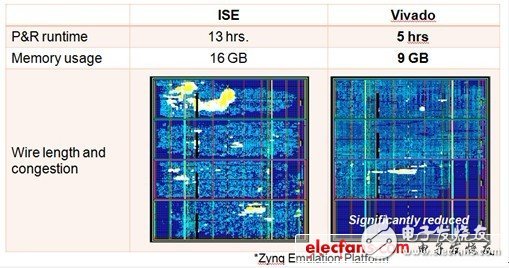

為展現(xiàn)這種優(yōu)勢(shì),賽靈思在 ISE設(shè)計(jì)套件和 Vivado 設(shè)計(jì)套件中用按鍵式流程方式同時(shí)運(yùn)行針對(duì)賽靈思 Zynq-7000 EPP 仿真平臺(tái)開(kāi)發(fā)的原始 RTL,同時(shí)將每種工具指向賽靈思世界最大容量的 FPGA 器件——采用堆疊硅片互聯(lián)技術(shù)的 Virtex-7 2000T FPGA。這樣 Vivado 設(shè)計(jì)套件的布局布線引擎僅耗時(shí) 5 個(gè)小時(shí)就完成了 120 萬(wàn)邏輯單元的布局,而 ISE 設(shè)計(jì)套件則耗時(shí)長(zhǎng)達(dá) 13 個(gè)小時(shí)(圖 2)。而且采用 Vivado 設(shè)計(jì)套件實(shí)現(xiàn)的設(shè)計(jì)擁塞明顯降低(設(shè)計(jì)中顯示為灰色和黃色的部分),器件占用面積較小,這說(shuō)明總體走線長(zhǎng)度縮短。Vivado 設(shè)計(jì)套件實(shí)現(xiàn)方案還體現(xiàn)出更出色的內(nèi)存編譯效率,僅用9GB就實(shí)現(xiàn)設(shè)計(jì)要求的內(nèi)存,而 ISE 設(shè)計(jì)套件則用了 16GB。

Feist 表示:“從本質(zhì)上來(lái)說(shuō), 你看到的就是 Vivado 設(shè)計(jì)套件在滿足所有約束條件下,實(shí)現(xiàn)整個(gè)設(shè)計(jì)只需占用 3/4 的器件資源。這意味著用戶(hù)可以為自己的設(shè)計(jì)添加更多的邏輯功能和片上存儲(chǔ)器,甚至可以采用更小型的器件。”

圖 2:Vivado 設(shè)計(jì)套件的多維分析算法可創(chuàng)建專(zhuān)門(mén)針對(duì)最佳時(shí)序、擁塞和走線長(zhǎng)度(而不僅僅只是針對(duì)最佳時(shí)序)優(yōu)化的布局。

功耗優(yōu)化和分析

當(dāng)今時(shí)代, 功耗是FPGA設(shè)計(jì)中最關(guān)鍵的環(huán)節(jié)之一。因此,Vivado設(shè)計(jì)套件的重點(diǎn)就是專(zhuān)注于利用先進(jìn)的功耗優(yōu)化技術(shù),為用戶(hù)的設(shè)計(jì)提供更大的功耗降低優(yōu)勢(shì)。“我們?cè)诩夹g(shù)上采用了目前在ASIC工具套件中可以見(jiàn)到的先進(jìn)的時(shí)鐘門(mén)控制技術(shù),通過(guò)該技術(shù)可以擁有設(shè)計(jì)邏輯分析的功能,同時(shí)消除不必要的翻轉(zhuǎn)”Feist表示 “具體來(lái)說(shuō),新的技術(shù)側(cè)重于翻轉(zhuǎn)因子 ‘a(chǎn)lpha’,它能夠降低30%的動(dòng)態(tài)功耗”Feist說(shuō),賽靈思去年在ISE設(shè)計(jì)套件中開(kāi)始應(yīng)用該技術(shù), 并一直沿用至今。 Vivado將繼續(xù)加強(qiáng)這一技術(shù)的應(yīng)用。

此外,有了這一新的可擴(kuò)展的數(shù)據(jù)共享模型,用戶(hù)可以在設(shè)計(jì)流程的每一個(gè)階段得到功耗的估值,從而可以在問(wèn)題發(fā)展的前期就能預(yù)先進(jìn)行分析, 從而能夠在設(shè)計(jì)流程中,先行解決問(wèn)題。

簡(jiǎn)化工程變更單(ECO)

增量流量讓快速處理小的設(shè)計(jì)更改成為可能,每次更改后只需重新實(shí)現(xiàn)設(shè)計(jì)的一小部分,使迭代速度更快。它們還能在每個(gè)增量變化之后實(shí)現(xiàn)性能的表現(xiàn),從而無(wú)需多個(gè)設(shè)計(jì)迭代。為此,Vivado設(shè)計(jì)套件還包括對(duì)一個(gè)流行的ISE FPGA編輯器工具的新的擴(kuò)展,稱(chēng)為Vivado器件編輯器。Feist說(shuō),在一個(gè)布局布線設(shè)計(jì)上使用Vivado器件編輯器,設(shè)計(jì)師現(xiàn)在有能力去做移動(dòng)單元, 重新布線, 連接一個(gè)寄存器輸出作為調(diào)試管腳, 修改DCM或者查找表(LUT)的參數(shù)的工程變更單(ECO)——在設(shè)計(jì)周期的后期,無(wú)需通過(guò)返回設(shè)計(jì)重新綜合和實(shí)現(xiàn)。他說(shuō),目前行業(yè)沒(méi)有任何其他FPGA設(shè)計(jì)環(huán)境可以提供這種級(jí)別的靈活性。

基于業(yè)界標(biāo)準(zhǔn)而打造

四年半前, 當(dāng)賽靈思開(kāi)始從頭打造Vivado設(shè)計(jì)套件的時(shí)候,架構(gòu)打造的首要任務(wù),就是用標(biāo)準(zhǔn)的設(shè)計(jì)環(huán)境代替專(zhuān)有格式。致力于打造一個(gè)開(kāi)放的環(huán)境,讓客戶(hù)能夠用 EDA 工具和第三方 IP 進(jìn)行擴(kuò)展。例如,Vivado 設(shè)計(jì)套件可支持 SDC(Synopsys 設(shè)計(jì)約束)、ARM AMBA AXI 4 IP互聯(lián)標(biāo)準(zhǔn)、IP-XACT IP封裝和交付標(biāo)準(zhǔn),并且在新環(huán)境中提供了強(qiáng)大的互動(dòng) TCL 腳本功能。。

流程自動(dòng)化,非流程強(qiáng)制化

在 Vivado 設(shè)計(jì)套件構(gòu)建過(guò)程中,賽靈思工具團(tuán)隊(duì)遵循這樣的原則“自動(dòng)化設(shè)計(jì)方式,不強(qiáng)制設(shè)計(jì)方式”。Feist 說(shuō):“不管用戶(hù)用 C、C++、SystemC、VHDL、Verilog、System Verilog、MATLAB 還是 Simulink 開(kāi)始編程,也不管他們用的是我們的 IP 還是第三方的 IP,我們提供了一種實(shí)現(xiàn)所有流程自動(dòng)化,幫助客戶(hù)提高生產(chǎn)力的方法。我們還充分考慮到我們的用戶(hù)的各種技能水平和偏好,既能滿足需要全按鍵式流程的客戶(hù)的要求,也能滿足在設(shè)計(jì)流程的每一步都進(jìn)行分析的客戶(hù)的要求,甚至還能滿足那些認(rèn)為用 GUI 的是低手,喜歡用 TCL 以命令行或批處理模式完成全部設(shè)計(jì)流程的客戶(hù)的要求。用戶(hù)能夠根據(jù)自己的特定需求,選用套件功能。”

為進(jìn)一步增強(qiáng)所有用戶(hù)的設(shè)計(jì)體驗(yàn),賽靈思在 Vivado 設(shè)計(jì)套件中加入了某些奇妙的新功能,同時(shí)為深受客戶(hù)贊譽(yù)的 FPGA 編輯器增加了芯片編輯器功能。

IP 封裝器、集成器和目錄

賽靈思的工具架構(gòu)團(tuán)隊(duì)把重點(diǎn)放在新套件專(zhuān)門(mén)的 IP 功能設(shè)計(jì)上,以便于 IP 的開(kāi)發(fā)、集成與存檔。為此,賽靈思開(kāi)發(fā)出了 IP 封裝器、IP 集成器和可擴(kuò)展 IP 目錄三種全新的 IP 功能。

Feist 表示:“今天很難找到不采用IP 的 IC 設(shè)計(jì)。我們采用業(yè)界標(biāo)準(zhǔn),提供專(zhuān)門(mén)便于 IP 開(kāi)發(fā)、集成和存檔/維護(hù)的工具,這都有助于我們生態(tài)系統(tǒng)合作伙伴中的 IP 廠商和客戶(hù)快速構(gòu)建 IP,提高設(shè)計(jì)生產(chǎn)力。目前已有 20 多家廠商提供支持該最新套件的 IP。”

采用 IP 封裝器,賽靈思的客戶(hù)、賽靈思公司自己的 IP 開(kāi)發(fā)人員和賽靈思生態(tài)環(huán)境合作伙伴可以在設(shè)計(jì)流程的任何階段將自己的部分設(shè)計(jì)或整個(gè)設(shè)計(jì)轉(zhuǎn)換為可重用的內(nèi)核,這里的設(shè)計(jì)可以是 RTL、網(wǎng)表、布局后的網(wǎng)表甚至是布局布線后的網(wǎng)表。IP 封裝器可以創(chuàng)建 IP 的 IP-XACT 描述,這樣用戶(hù)使用新型 IP 集成器就能方便地將 IP 集成到未來(lái)設(shè)計(jì)中。IP 封裝器在 XML 文件中設(shè)定了每個(gè) IP 的數(shù)據(jù)。Feist 說(shuō)一旦 IP 封裝完成,用 IP 集成器功能就可以將 IP 集成到設(shè)計(jì)的其余部分。

Feist 說(shuō):“IP 集成器可以讓客戶(hù)在互聯(lián)層面而非引腳層面將 IP 集成到自己的設(shè)計(jì)中。可以將 IP 逐個(gè)拖放到自己的設(shè)計(jì)圖(canvas)上,IP 集成器會(huì)自動(dòng)提前檢查對(duì)應(yīng)的接口是否兼容。如果兼容,就可以在內(nèi)核間劃一條線,然后集成器會(huì)自動(dòng)編寫(xiě)連接所有引腳的具體 RTL。”

Feist 表示:“這里的重點(diǎn)是可以取出已用 IP 集成器集成的四五個(gè)模塊的輸出,然后通過(guò)封裝器再封裝。這樣就成了一個(gè)其他人可以重新使用的 IP。這種 IP 不一定必須是 RTL,可以是布局后的網(wǎng)表,甚至可以是布局布線后的網(wǎng)表模塊。這樣可以進(jìn)一步節(jié)省集成和驗(yàn)證時(shí)間。”

第三大功能是可擴(kuò)展 IP 目錄,它使用戶(hù)能夠用他們自己創(chuàng)建的 IP 以及賽靈思和第三方廠商許可的 IP 創(chuàng)建自己的標(biāo)準(zhǔn) IP 庫(kù)。賽靈思按照 IP-XACT 標(biāo)準(zhǔn)要求創(chuàng)建的該目錄能夠讓設(shè)計(jì)團(tuán)隊(duì)乃至企業(yè)更好的組織自己的 IP,供整個(gè)機(jī)構(gòu)共享使用。Feist 稱(chēng)賽靈思系統(tǒng)生成器 (System Generator) 和 IP 集成器均已與Vivado 可擴(kuò)展 IP 目錄集成,故用戶(hù)可以輕松訪問(wèn)編目 IP 并將其集成到自己的設(shè)計(jì)項(xiàng)目中。

Vivado 產(chǎn)品營(yíng)銷(xiāo)總監(jiān) Ramine Roane指出:“以前第三方 IP 廠商用 Zip 文件交付的IP格式各異,而現(xiàn)在他們交付的 IP,不僅格式統(tǒng)一,可立即使用,而且還與 Vivado 套件兼容。”

Vivado HLS 把 ELS帶入 主流

可能 Vivado 設(shè)計(jì)套件采用的眾多新技術(shù)中,最具有前瞻性的要數(shù)新的 Vivado HLS(高層次綜合)技術(shù),這是賽靈思 2010 年收購(gòu) AutoESL 后獲得的。在收購(gòu)這項(xiàng)業(yè)界最佳技術(shù)之前,賽靈思對(duì)商用 ESL 解決方案進(jìn)行了廣泛評(píng)估。市場(chǎng)調(diào)研公司 BDTI 的研究結(jié)果幫助賽靈思做出了收購(gòu)決策(見(jiàn) 賽靈思中國(guó)通訊雜志第 36 期“BDTI研究認(rèn)證以DSP為核心的FPGA設(shè)計(jì)的高層次綜合流程 ” http://china.xilinx.com/china/xcell/xl36/2-7.pdf)。

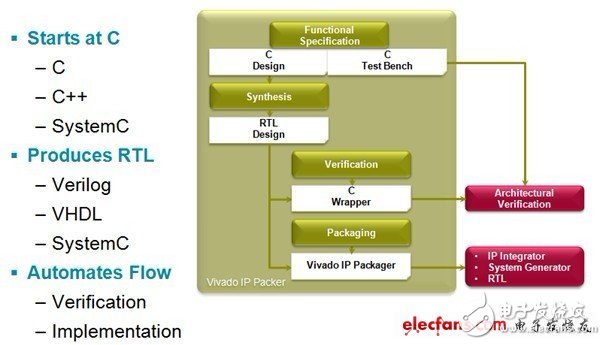

Feist 表示:“Vivado HLS 全面覆蓋 C、C++、SystemC,能夠進(jìn)行浮點(diǎn)運(yùn)算和任意精度浮點(diǎn)運(yùn)算。這意味著只要用戶(hù)愿意,可以在算法開(kāi)發(fā)環(huán)境而不是典型的硬件開(kāi)發(fā)環(huán)境中使用該工具。這樣做的優(yōu)點(diǎn)在于在這個(gè)層面開(kāi)發(fā)的算法的驗(yàn)證速度比在 RTL 級(jí)有數(shù)量級(jí)的提高。這就是說(shuō),既可以讓算法提速,又可以探索算法的可行性,并且能夠在架構(gòu)級(jí)實(shí)現(xiàn)吞吐量、時(shí)延和功耗的權(quán)衡取舍。”

設(shè)計(jì)人員使用 Vivado HLS 工具可以通過(guò)各種方式執(zhí)行各種功能。為了演示方便,F(xiàn)eist 講解了用戶(hù)如何通過(guò)一個(gè)通用的流程進(jìn)行 Vivado HLS 開(kāi)發(fā) IP 并將其集成到自己的設(shè)計(jì)當(dāng)中。

在這個(gè)流程中,用戶(hù)先創(chuàng)建一個(gè)設(shè)計(jì) C、C++ 或 SystemC 表達(dá)式,以及一個(gè)用于描述期望的設(shè)計(jì)行為的 C 測(cè)試平臺(tái)。隨后用 GCC/G++或 Visual C++ 仿真器驗(yàn)證設(shè)計(jì)的系統(tǒng)行為。一旦行為設(shè)計(jì)運(yùn)行良好,對(duì)應(yīng)的測(cè)試臺(tái)的問(wèn)題全部解決,就可以通過(guò) Vivado HLS Synthesis 運(yùn)行設(shè)計(jì),生成 RTL 設(shè)計(jì),代碼可以是 Verilog,也可以是 VHDL。有了 RTL 后,隨即可以執(zhí)行設(shè)計(jì)的 Verilog 或 VHDL 仿真,或使用工具的 C封裝器技術(shù)創(chuàng)建 SystemC 版本。然后可以進(jìn)行System C架構(gòu)級(jí)仿真,進(jìn)一步根據(jù)之前創(chuàng)建的 C 測(cè)試平臺(tái),驗(yàn)證設(shè)計(jì)的架構(gòu)行為和功能。

設(shè)計(jì)固化后,就可以通過(guò) Vivado 設(shè)計(jì)套件的物理實(shí)現(xiàn)流程來(lái)運(yùn)行設(shè)計(jì),將設(shè)計(jì)編程到器件上,在硬件中運(yùn)行和/或使用 IP 封裝器將設(shè)計(jì)轉(zhuǎn)為可重用的 IP。隨后使用 IP 集成器將 IP 集成到設(shè)計(jì)中,或在系統(tǒng)生成器 (System Generator) 中運(yùn)行 IP。

圖三 – Vivado HLS 支持設(shè)計(jì)團(tuán)隊(duì)直接從系統(tǒng)級(jí)開(kāi)始他們的設(shè)計(jì)。

這只是使用該工具的方法之一。實(shí)際上在即將發(fā)行的賽靈思Xcell雜志中,安捷倫的 Nathan Jachimiec 和賽靈思的 Fernando Marinez Vallina 將介紹如何使用 Vivado HLS 技術(shù)(在 ISE設(shè)計(jì)套件的流程中稱(chēng)為 AutoESL 技術(shù))為安捷倫開(kāi)發(fā) UDP 包引擎。

VIVADO 仿真器

除了 Vivado HLS,公司還為該套件新開(kāi)發(fā)了一種同時(shí)支持 Verilog 和 VHDL 的混合語(yǔ)言仿真器。Feist 表示,只需要單擊鼠標(biāo),用戶(hù)就可以啟動(dòng)行為仿真,然后從集成波形查看器中查看結(jié)果。通過(guò)采用最新性能優(yōu)化的仿真內(nèi)核,可加速行為級(jí)仿真速度,執(zhí)行速度比賽靈思 ISE 設(shè)計(jì)套件仿真器快三倍。采用硬件協(xié)仿真,門(mén)級(jí)仿真速度則可加快 100 倍。

2012供貨情況

之前賽靈思ISE 設(shè)計(jì)套件針對(duì)不同類(lèi)型設(shè)計(jì)者(邏輯,嵌入式, DSP和系統(tǒng))所發(fā)行的四個(gè)版本, 賽靈思將推出Vivado 設(shè)計(jì)套件的兩個(gè)版本。其中, Vivado 基礎(chǔ)設(shè)計(jì)版本包括新型 IP 工具和Vivado的綜合-比特流流程。而 Vivado 系統(tǒng)版本則包括設(shè)計(jì)版本的所有工具、系統(tǒng)生成器和賽靈思的最新 Vivado HLS 工具。

Vivado 設(shè)計(jì)套件 2012.1 版本目前已隨早期試用計(jì)劃推出。如需了解更多詳情,敬請(qǐng)聯(lián)系您所在地的賽靈思代表。2012.2 版本將于第二季度中期公開(kāi)發(fā)布,今年晚些時(shí)候還將推出 WebPACK。目前支持服務(wù)尚未到期的 ISE 設(shè)計(jì)套件用戶(hù)除了ISE之外,將免費(fèi)得到全新的 Vivado 設(shè)計(jì)套件。

對(duì)使用 28nm 器件之前器件的用戶(hù),賽靈思將繼續(xù)提供對(duì) ISE 設(shè)計(jì)套件的支持。

賽靈思vivado設(shè)計(jì)套件專(zhuān)題:http://www.nxhydt.com/topic/tech/vivado/

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論