晶振 PCB設計

印制電路板(PCB)是電子產品中電路元件和器件的支撐件.它提供電路元件和器件之間的電氣連接。隨著電于技術的飛速發展,PCB的密度越來越高。PCB設計的好壞對抗干擾能力影響很大.因此,在進行PCB設計時.必須遵守PCB設計的一般原則,并應符合抗干擾設計的要求。首先,要考慮PCB尺寸大小。PCB尺寸過大時,印制線條長,阻抗增加,抗噪聲能力下降,成本也增加;過小,則散熱不好,且鄰近線條易受干擾。在確定PCB尺寸后.再確定特殊元件的位置。最后,根據電路的功能單元,對電路的全部元器件進行布局。

?

時鐘源通常是系統中最嚴重的EMI輻射源,如果接長線,其結果是長線就成了天線,這在很多應用中是不準許的,所有時鐘源都必須盡量靠近相關器件,必要時用多個時鐘源,不得以下可以采用多層PCB將時鐘連線屏蔽(但這種方法只有在不得以下為之,而且成本未必低于多時鐘(多層PCB的價格明顯高于雙面板),要過某些強制標準的產品盡量不要這么干)。有源晶振的輸出一般是標準TTL規格,至于能驅動多少芯片要看這些芯片的特性。

晶振和芯片的距離一般要盡量靠近,一般指的是無源晶振,那么有源的晶振布線有什么要求嗎?有源晶振能驅動多少個芯片呢?

有源晶振也不能輸出接長線

時鐘源通常是系統中最嚴重的EMI輻射源,如果接長線,其結果是長線就成了天線,這在很多應用中是不準許的,所有時鐘源都必須盡量靠近相關器件,必要時用多個時鐘源,不得以下可以采用多層PCB將時鐘連線屏蔽。有源晶振的輸出一般是標準TTL規格,至于能驅動多少芯片要看這些芯片的特性。

時鐘布哪一層?

夾心層,其上下都是覆地

但這種方法只有在不得以下為之,而且成本未必低于多時鐘(多層PCB的價格明顯高于雙面板),要過某些強制標準的產品盡量不要這么干。

1. Crystal下不可走線,電路儘量靠近chip端。

2. trace儘量短,與其他信號需20mil間距,最好使用ground trace與其他信號隔離。

3.Crystal底下儘量不要走線。 如果實在要走線的話, 不能走線進Crystal pin腳周圍50mil之內。 尤其避免高速訊號。

晶振信號線盡可能短,需要包地(因為有噪聲,本質就是怕它影響到別人,或者怕別人影響到他)。盡可能不穿孔,以為一個過孔會有0.5pF的寄生電容,另外,走線粗細要一致

晶振的選擇和PCB布局(一)

晶體的選擇和PCB板布局會對VCXO、CLK發生器的性能參數產生一定的影響。選擇晶體時,除了頻率、封裝、精度和工作溫度范圍,在VCXO應用中還應注意等效串聯電阻和負載電容。串聯電阻導致晶體的功耗增大。阻值越低,振蕩器越容易起振。

負載電容是晶體的一個重要參數,首先,它決定了晶體的諧振頻率。一般晶體的標稱頻率指的是其并聯指定負載電容后的諧振頻率。應當指出,此處的標稱頻率是當CL等于指定負載電容時利用公式(1)計算出的值,但不是利用計算出的值。

因此,VCXO的調諧范圍與CL的值緊密相關。當負載電容值較小時,VCXO的調諧范圍限制在上端;同樣,電容值較大時,調諧范圍將限制在下端。負載電容的適當取值取決于VCXO的特性。例如,MAX9485設計中,為了均衡調諧范圍、調諧曲線中點、同時簡化電路板設計,我們選擇Ecliptek (ECX-5527-27)具有14pf負載電容的27MHz晶體。

使用這樣的晶體時,MAX9485具有±200ppm的牽引范圍。應該指出,封裝會導致晶體牽引范圍的差異。一般金屬殼封裝比表貼器件(SMD)的牽引范圍更大。但是最近DAISHINKU公司生產的一款新SMD晶體可達到與金屬殼晶體近似的牽引范圍。我們測試了這款SMD晶體(DSX530GA),發現外接兩個4pf的并聯電容時可以實現±200ppm頻率牽引范圍。

晶振的選擇和PCB布局(二)

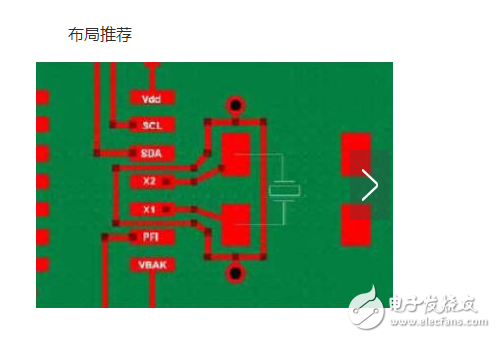

為了限制VCXO的調諧范圍,可通過改變外部并聯電容設置向上的調節范圍。并聯電容取值范圍為4 - 7pf,取決于電路板寄生電容。另一方面,向下的調節范圍取決于內部變容二極管值,不能由外部改變。為了降低寄生電容對向上頻率調節范圍的影響,在電路板布局中應盡可能的減少晶體引腳對地的寄生電容,保證引腳與地層和電源層之間的清潔。

1. X1 和X2 晶體引腳均為高阻引腳,必須小心處理。需確保晶體與X1,X2 引腳之間的連線距離最短,必須小于5mm。

2. 確保VDD引腳具有良好的退藕性。(VDD與地之間連接一個0.1uF電容)

3. 即使信號位于板內層,也不能允許信號線靠近X1 和X2 引腳。在晶體引腳周圍使用接地保護環。在內部或板反面使用接地保護敷銅。目前有很多表面封裝晶體可用。應當注意:通過圖中示意的孔將保護環與地相連。

1. Crystal下不可走線,電路儘量靠近chip端,并且與其輸出時鐘相關的時鐘線走線等長,等阻抗。

2. trace儘量短,與其他信號需20mil間距,最好使用ground trace與其他信號隔離。

3.Crystal底下儘量不要走線。 如果實在要走線的話, 不能走線進Crystal pin腳周圍50mil之內。 尤其避免高速訊號。

系統中最復雜的部分是時鐘,100M頻率對時鐘來說是200M。

FPGA的時鐘輸入要使用全局時鐘引腳。高熱下時鐘漂移,要加鎖相環同步電路。FPGA全部用同步設計,不直接用組合邏輯。

晶振參考最小化設計,電源部分需要加磁珠和小電容去耦,輸出加始端匹配(頻率不高就不用加匹配,遠端有時也要加匹配,防反射,PCI除外),晶振下面鋪數字地,多打孔,孔挨著pin。

時鐘走線要看你采用什么分配方案。是公共時鐘同步還是源時鐘同步,要不要加時鐘分配器件,加幾級驅動。

實際走線長短根據分配方案和拓撲結構具體計算(盡量偏短),時鐘分配器件下要鋪銅,未用引腳用1K電阻下拉到地。多級驅動要加PLL補償(補償值需要計算)。

國產133M及以上晶振不可靠,可以從33M倍頻產生133M,這樣好選材。要么選日本貨等。

時鐘輸出最好不分叉,實在不行最多分兩路(特指低速,高速必須點對點),其他情況必須加時鐘驅動。時鐘驅動最多帶2個負載,分叉后相位可能跑偏。

在布局上,時鐘電路周圍走低速低壓信號電路,遠離電源,約束在同層走線,保證阻抗連續,盡量走在少受干擾的內層,晶振不要靠近板邊。走等長線的部分周圍要留出足夠的空間(注意3W規則,100M以上時鐘線必須拉圓弧線)。點對點、菊花鏈結構最常用。晶振下最好不走線,尤其是高速信號線。注意大電容焊盤的特殊處理,要求保證大電流供電能力。

總之,時鐘是關鍵信號線,所有安排一律從優,要特殊照顧。

1.有正弦波輸出的貼片晶振,輸出負載為10k;如果10k的負載能力不夠,必須加緩沖電路,使PLL的參考與單片機的時鐘相隔離;

2.晶振輸出到PLL的信號線不能長,再加上TTL電平,輻射太厲害了;

3.晶振PCB表面鋪地,周圍通過過孔與底層大面積地相連;

4.晶振輸出接帶通濾波器,PLL輸出接帶通濾波器;

5.對兩個PLL分別進行屏蔽;晶振輸出接兩個PLL,很難把信號線走短,最好是用同軸線從底層連接。

6.主要是做好屏蔽,尤其是接收電路部分,不光要屏蔽,還要考慮接地;

a)緩沖電路是指在你的晶振負載能力很弱的情況下使用,提高驅動能力,還起到隔離的效果,由于你現在使用TTL輸出電平的晶振,驅動能力強,而且能改善PLL的帶內噪聲,所以可以不加緩沖放大器,主要是要解決輻射干擾問題;如果有板子上地方,也可以加一個簡單的晶體管限幅放大器,會有點好處。

b)一般超短波頻段和微波頻段,射頻前端均是收發開關或雙工器-濾波器-LNA-濾波器-混頻模式;短波一般是收發開關-濾波器-混頻模式。

c)晶振輸出,我做過實驗,采用普通的陶瓷濾波器進行濾波,效果是有改善,不過還是不是很理想。 所以我才采用電容強拉波形.