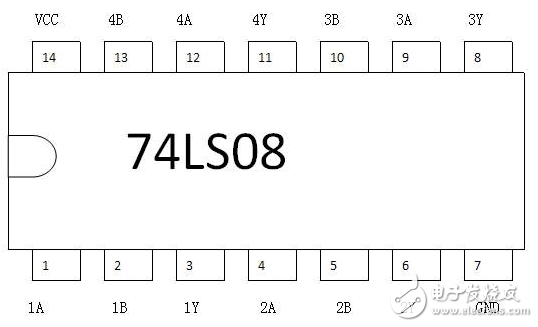

74LS08:與門,詳細地說是4二輸入與門,即一片74LS08芯片內有共四路二個輸入端的與門。

74LS08引腳圖

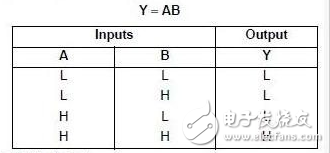

74LS08真值表

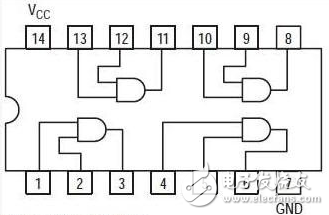

74LS08邏輯圖

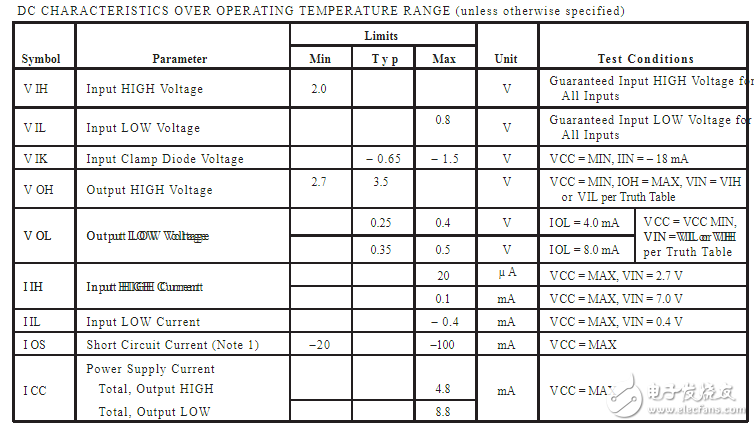

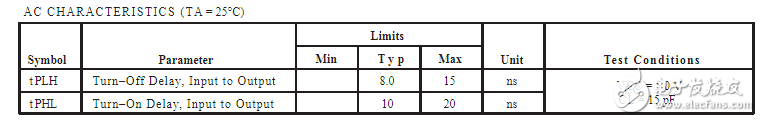

74LS08電氣參數

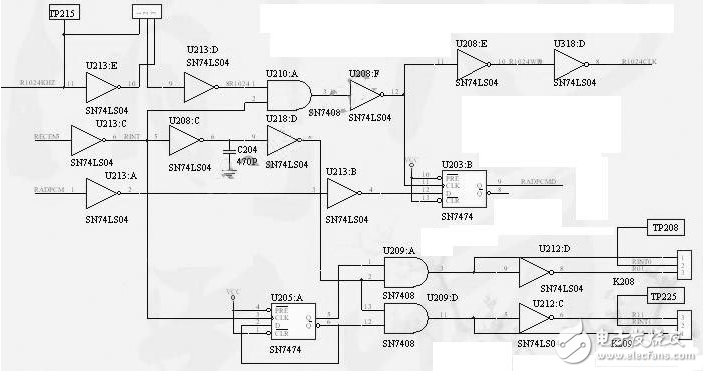

74LS08應用電路(一)

接收定時信號產生電路

從圖中可知,同發送定時信號類同,產生定時信號的方法也相同,故波形略。需要指出的是,U213:A、B(74LS04)、U203:B(74LS74)的作用是對接收到的數字基帶信號進行整形輸出。

U213:D、E(74LS04)、U210:A(74LS08)、U208:D、E(74LS08)的作用是用接收使能信號(由軟件產生)對接收時鐘1024KHz的選通進行輸出。

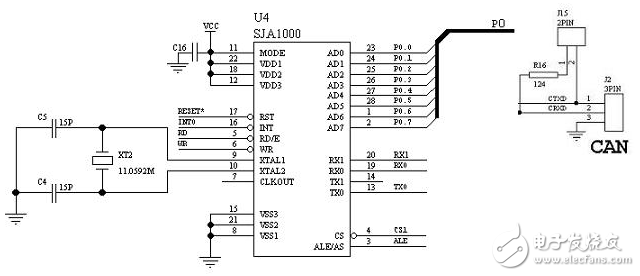

74LS08應用電路(二)

CAN控制器選擇了Philips公司生產的SJA1000芯片,電路如圖1所示。SJA1000是既支持CAN2.0A又支持CAN2.0B的CAN控制器,它與僅支持PCA82C2000在硬件和軟件上完全兼容。

圖1CAN控制器電路

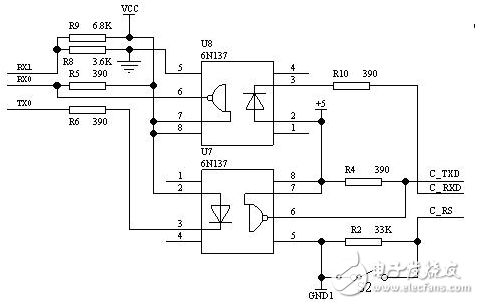

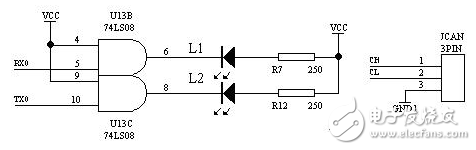

為了提高系統的抗干擾能力,在CAN控制器和CAN驅動器之間加入了使用高速光電隔離器件6N137構成的隔離電路,如圖2所示。

圖2 光電隔離電路

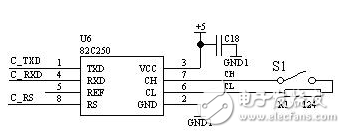

CAN總線收發器采用了PCA82C250,電路如圖3所示。PCA82C250是CAN控制器和物理總線間的接口,提供對總線的差動發送能力和對CAN控制器的差動接收能力,它與ISO11898標準兼容,有高速、斜率控制和待機三種工作方式,可根據實際情況選擇。

圖3 CAN收發器電路

CAN通信的指示及接口電路如圖4所示。其中與門74LS08是為了提高驅動能力而采用的。

圖4 CAN通信指示及接口電路

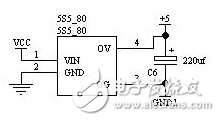

DC/DC電源隔離轉換和濾波電路為CAN通信接口電路提供電源,并實現與內部電路的隔離,電路如圖5所示。

圖5 DC/DC電源隔離轉換和濾波電路

74LS08應用電路(三)

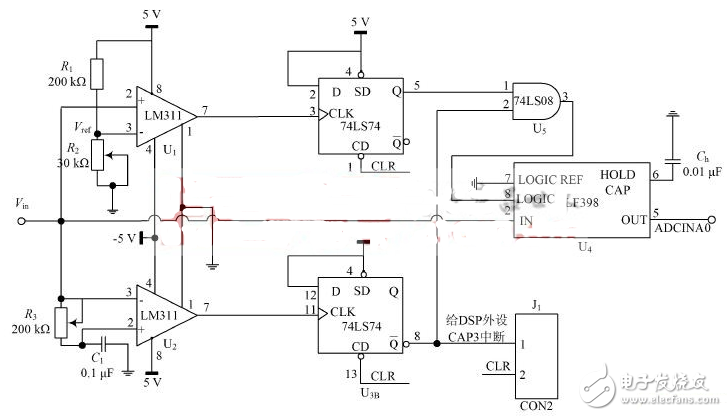

經過主放大電路處理后的脈沖信號雖然幅度較為理想,但脈沖寬度仍然較小,最小脈寬只有1ms.而A/D轉換需要一定的時間,要采到脈沖的尖峰需要對峰值電壓進行保持,同時向DSP提出中斷請求信號,使DSP響應中斷并啟動A/D轉換,轉換結束后DSP使采樣保持器復原為采樣狀態,實現系統的邏輯控制,本文設計的峰值保持電路如圖所示。

如圖5所示,U4是芯片LF398,它是美國半導體公司研制的集成采樣保持器。它只需外接一個保持電容就能完成采樣保持功能,其采樣保持控制端可直接接于TTL,CMOS邏輯電平。U1和U2是高速電壓比較器LM311,U3是上升沿觸發的雙D觸發器,U5是與門74LS08.經過主放大電路處理后的脈沖信號一路輸入到閾值比較器U1,另一路輸入到由比較器U2組成的峰值檢測電路(R3C1組成延遲電路與U2反向輸入端輸入的脈沖信號進行比較,用于判斷脈沖信號的峰值是否到來),還有一路輸入到采樣保持器LF398,而且LF398的輸出接到DSP內ADC模塊的ADCINA0引腳上。

當電壓脈沖信號幅度大于閾值電壓Vref(調試過程中設定Vref為0.5V,電壓低于0.5V的即可認為是噪聲而不予考慮),比較器U1輸出高電平,產生上升沿,上升沿再觸發U3A,它的Q端輸出高電平和峰值未來到時U3B的Qˉ端相與得高電平,去控制LF398的采樣控制端進入采樣狀態。當脈沖信號到達峰值后,比較器U2輸出高電平,得到上升沿,上升沿再觸發U3B,它的Qˉ端輸出低電平,U5輸出低電平,LF398進入保持狀態。U3B的Qˉ端輸出的下降沿作為DSP捕獲單元CAP3中斷的啟動信號,CAP3發出信號去啟動ADC,當A/D轉換結束后,DSP的GPIO口輸出一個低電平作為U3的清零信號CLR,雙D觸發器74LS74清零后,LF398的采樣控制端重新進入采樣狀態,準備保持下一個脈沖的峰值。