: 在電路中的某些模塊進入休眠或者空閑模式時,我們可以使用之前講過的Clock Gating技術來降低它們的動態功耗,但是無法降低它們的靜態功耗。而Power/Ground Gating技術可以在它們休眠的時候完全關掉它們的電源從而消除它們的靜態功耗。 理想情況下,Power gating可以完全消除

2020-09-16 16:04:15 10567

10567

本人在畫一個電容式按鍵控制的智能燈,現在在畫觸摸部分,白色線內的部分(明顯有薄薄的一層)不知道怎樣在AD中畫這薄薄的一層(把它當作什么來畫)。希望大神能給些意見或者建議。

2018-06-20 17:31:09

動態功耗調節介紹

2021-02-05 07:12:25

需求來說,eSR具有更好的圖像質量-推理速度均衡。彌補經典與深度學習上采樣之間的空白對于大量采用該技術非常重要。 本文貢獻包含以下幾點: 提出了幾種一層架構以彌補經典與深度學習上采樣之間的空白

2023-03-06 14:05:36

降低一個MCU的主頻就能降低運行的功耗嗎

2023-10-11 08:15:48

降低FPGA功耗的設計技術 Design Techniques to Reduce Power Consumption Each generation of FPGAs gets

2009-12-18 16:49:59

設計技巧為什么能夠節省功耗?降低FPGA功耗的設計技巧有哪些?

2021-04-30 06:04:19

低功耗∑-Δ產品的演變,以幫助說明所實現的信號鏈集成的完整性,并突出強調這給我們測量能力帶來的需求和進步。我們現在希望讓SiP(系統化封裝)、微型模塊和模塊更上一層樓,客戶將再次向我們提出新的測量挑戰

2018-10-23 14:18:35

AD在復制整塊PCB后,如何在粘貼時只粘貼某一層或某幾層?

2019-09-12 16:01:25

Altium 中怎么將焊盤蓋上一層油,不讓畫出來的焊盤裸露?就像下圖所示一樣

2016-10-21 22:02:36

FPGA功耗的基本概念,如何降低FPGA功耗?IGLOO能夠做到如此低的功耗是因為什么?

2021-04-30 06:08:49

技術亞閾值漏電流是靜態功耗產生的主要原因之一,降低亞閾值漏電流將有效地降低芯片的靜態功耗。亞閾值漏電流的解析模型如下公式所示:Vt為閾值電壓,n為亞閾值擺幅系數,W為晶體管的寬度,L為長度,μ為電子

2020-04-28 08:00:00

。除此之外,設計中采用一些低功耗技巧,也可以降低靜態功耗。IGLOO具有功耗友好的器件架構,能提供靜態、睡眠、Flash*Freeze功耗模式,允許采用動態電壓和頻率調節技術來降低系統整體實際功耗。提供可選擇

2019-07-05 07:19:19

綜合過程中功耗減少的補充。 值得注意的是,功耗是一個"機會均等"問題,從早期設計取舍到自動物理功耗優化,所有降低功耗的技術都彼此相互補充,并且需要作為每個現代設計流程中的一部分加以

2017-06-29 16:46:52

PADS layout中,這里說的可以走線什么意思,每一層不都是可以走線的嗎?

2019-04-11 08:36:41

PADS9.5 LAYOUT 設置元件 怎樣 可以重疊放置 大的中間小的 同一層的?

2017-08-04 15:39:15

PADS設計4板,第一層基板挖一個大矩形槽,露出第二層基板,再在第二層基板挖一個小矩形槽,嵌套的。請問怎么實現?

2023-03-24 11:16:33

接地層上的ADC。兩層之間的接地噪聲直接添加到時鐘信號,并產生過度抖動。抖動可造成信噪比降低,還會產生干擾諧波。圖7. 從數模接地層進行采樣時鐘分配。混合信號接地的困惑根源大多數ADC、DAC和其他混合

2014-11-20 10:58:30

如題,想要計算內外層每一層的敷銅面積,有沒有什么計算方法或者小工具可以使用?有些板子有敷銅百分比硬性要求。

2021-02-23 15:01:28

請問誰知道pcb覆銅在哪一層?

2019-11-05 16:51:51

pcb只顯示一層是怎么回事呢

2019-08-16 00:54:47

那一層透明的我不知道按到什么了,怎么關閉啊

2019-08-16 05:35:09

為什么在同一層鋪動態銅皮,有的可以自動避讓有的就沒有呢?

2019-07-23 05:35:22

為什么多晶硅柵上還要再摞一層鎢?不用不行嗎? 求大蝦指點

2012-01-12 17:22:54

正常情況下打開封裝庫文件像頂層絲層,焊盤層,底層絲印層,都會同時顯示出來。現在我在打開封裝庫文件時只能顯示一層,其他層面不能同時顯示出來,這是為什么?所有的層面都有打開啊???

2012-08-11 15:05:37

本帖最后由 eehome 于 2013-1-5 09:54 編輯

為什么有的人做PCB封裝時要加一層機械層1的網狀物?這樣做有什么作用嗎?做成的PCB上也沒有顯示啊?

2012-08-23 11:50:22

1、畫線時,一直怎么在第一層上,怎么切換,怎么設置;2、畫線時,同時放置焊盤,怎么快捷操作,謝謝指點下。

2019-08-13 22:44:23

大大降低系統功耗,這可以從單片機的供電電壓、內部結構、系統時鐘和低功耗模式等幾方面來考察一款單片機的低功耗特性。一般來講,用戶在選擇技術供應商和產品過程中,需要對下面的一些重要硬件參數進行更加深入的考量:

2019-06-20 08:06:05

公司最近開發電池供電的低功耗模塊,萬用表示波器很難測出動態電流,真心問問做低功耗或者穿戴設備方面的工程師或者測試設備技術廠家技術人員或者各路“牛”,你們用什么設備測試?動態定電流范圍較大ua - 幾十毫安,變化速率快

2015-01-10 22:53:53

的基于使用頻率的狀態機值的選擇等。 為了更好地理解本文將要討論的設計技巧為什么能夠節省功耗,我們先對功耗做一個簡單介紹。 功耗包含兩個因素:動態功耗和靜態功耗。動態功耗是指對器件內的容性負載充放電所需

2012-01-11 11:59:44

請問做單面板元件庫時元件面的絲印和焊接面的絲印分別放在哪一層?一些注解文字放在哪一層?

2011-12-13 13:59:13

市場上已有的解決方案,以降低開發成本。在當今對成本和功耗都非常敏感的“綠色”環境下,對于高技術企業,兩種挑戰都有什么影響呢?第一種挑戰意味著開發全新的產品,其功能是獨一無二的,具有較低的價格以及較低

2019-08-09 07:41:27

單片機的本質只是一個工具。因此,更為重要的是模擬電子,數字電子以及其它基礎的專業課程。第一層 : 我來了第二層 真的打呀第三層 并肩作戰,時間,說愛你不容易第四層 狀態,你在哪里第五層 時間,還是

2015-11-01 08:50:35

第一層 : 我來了處在這一層的典型是可以用C語言寫簡單的邏輯控制,如閃爍LED,簡單數碼管顯示,簡單外圍模塊驅動實驗。一般對單片機感興趣,經常動手實踐的人,半年左右,可以練到此地步(針對沒有接觸過

2018-03-22 11:46:51

第一層 : 我來了處在這一層的典型是可以用C語言寫簡單的邏輯控制,如閃爍LED,簡單數碼管顯示,簡單外圍模塊驅動實驗。一般對單片機感興趣,經常動手實踐的人,半年左右,可以練到此地步(針對沒有接觸過

2018-09-07 10:13:49

在一個平面上鋪一層銅和鋪兩層銅最后的實際厚度是多少。是兩倍的關系還是說是一樣的厚度,因為考慮到要過大電流,線寬不是很大。

2015-12-23 10:36:38

FPGA的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低,如同其它多數事物一樣,降低功耗的設計就是一種協調和平衡藝術,在進行低功耗器件的設計時,人們必須仔細權衡性能、易用性、成本、密度以及功率等諸多指標。

2019-08-15 08:28:42

低功耗mcu的選擇方法如何降低mcu的功耗

2021-02-24 06:11:07

多層板的某一層中,如何刪除一部分負片?因為這部分附近有高壓,擔心高壓會有影響,所以想刪掉這附近的負片。

2019-08-22 04:24:44

復雜器件專業技術相結合,將為系統供應商提供低功耗的芯片方案,供他們在此基礎上持續提高帶寬容量,并完成更智能的處理。此外,TPACK提供的芯片解決方案可以導入到最新的FPGA中,進一步降低功耗。最終實現

2019-07-31 07:13:26

AD中畫PCB板時如何將某一層調為高亮?

2019-08-02 05:35:13

易失性FPGA的電源特性是什么?如何在進行板級設計時,降低系統的靜態與動態功耗?

2021-04-08 06:47:53

請問如何添加一層機械層?謝謝

2019-09-17 02:56:08

如何采用創新降耗技術應對FPGA靜態和動態功耗的挑戰?

2021-04-30 07:00:17

節省功耗的特性的實現和各種最少功耗數據存儲技術的實現。除此之外,設計中采用一些低功耗技巧,也可以降低靜態功耗。 IGLOO具有功耗友好的器件架構,能提供靜態、睡眠、Flash*Freeze功耗模式

2020-05-13 08:00:00

高低電平翻轉跳變沿期間,電流很大,存在較大功耗,所以,降低硬件電路功耗主要是降低電路動態功耗。 (3)采用多CPU系統 盡管現在已有各種可在不過多加重功耗負擔的前提下提高性能的技術,但用一個芯片

2020-07-08 15:52:10

,以降低功耗。然而,門控時鐘易引起毛刺,必須對信號的時序加以嚴格限制,并對其進行仔細的時序驗證。 另一種常用的時鐘技術就是可變頻率時鐘。它根據系統性能要求,配置適當的時鐘頻率以避免不必要的功耗。門控

2016-06-29 11:28:15

從當前嵌入式消費電子產品來看,媒體處理與無線通信、3D游戲逐漸融合,其強大的功能帶來了芯片處理能力的增加,在復雜的移動應用環境中,功耗正在大幅度增加。比如手機,用戶往往希望待機時間、聽音樂時間,以及看MPEG4時間能更長。在這樣的背景下,如何降低入式芯片的功耗已迫在眉睫。

2019-08-28 08:27:58

可以做哪些措施來降低功耗

2023-10-23 07:51:09

自己做了一個電路板,因為功耗除了點問題,怎么降低電路板功耗呢

2019-08-07 22:21:34

圖中控件快捷菜單有3層,第一層“3”,第二層“3.2”,第三層“3.2.1”“3.2.2”,通過事件結構里面的“快捷菜單選擇”只能觸發最后一層的“3.2.1”“3.2.2”,能不能實現第二層和第三層都可以觸發?也就是點“3.2”能觸發事件,點“3.2.1”也能觸發事件

2016-04-14 10:06:36

請問PADS 中金手指部分放在那一層里。是不和鍍錫層一個層啊!solderMaks

2012-11-05 08:25:29

請問PADS 中金手指部分放在那一層里。是不和鍍錫層一個層啊!solderMaks

2012-11-05 08:38:17

功耗:(1)使用clock gating 技術減小活動因子是降低翻轉功耗的辦法之一,這個方法已經很成熟,易于采用;(2) 減小毛刺Glitch減少毛刺會使活動因子變小,進而幫助降低功耗;競爭和冒險

2022-06-09 18:06:15

集電極層中雜質濃度的降低,這有助于抑制空穴注入(2)。SiC-SBD在反向恢復和導通損耗方面的改進通過使用SiC-SBD,高速混合模塊可以將反向恢復峰值電流降低約60%。SiC-SBD是不帶少數

2020-09-02 15:49:13

人們對低功耗設備和設計技術的興趣激增。通過回顧已提出的降低功耗的技術,深入了解低功耗設計中的一些基本權衡。設計的主要策略是以速度換取功耗,不浪費功耗,并找到一個較低的功耗問題。 文章通過定義

2020-07-07 11:40:06

的重新安排卻只能降低5%的翻轉次數。在不同的低功耗設計層次,考慮的重點也不相同。比如說只有在工藝級設計時,設計者才考慮通過擴散區的摻雜濃度來影響閾值電壓。近年來,降低功耗的技術逐漸從電路層向結構層,從

2013-05-16 20:00:33

文檔里說CLA 沒有堆棧,不支持函數的嵌套,那請問CLA只允許調用一層函數嗎?

2020-07-19 13:49:39

請問FPGA與DDR3是否必須在同一層放置,由于現在不在同一層,軟件調試的時候圖像有抖動,軟件說是因為FPGA與DDR3未在同一層,導致時序有問題。

2018-12-26 09:37:37

什么是TICKLESS?怎么能實現功耗的降低呢?TICKLESS是如何去實現功耗降低的呢?

2022-02-24 08:02:02

pcb裸銅的logo放在哪一層?

2023-10-16 07:29:19

PCB中不在同一層的線形成銳角有關系嗎?硬件工程師 說不能這樣走,但是我的想法是又不在同一層為什么不能?

2019-05-21 10:00:46

圖一是視頻里面的,圖二是我自己做的。請問如何像圖一一樣顯示一層?不顯示背面的?還有怎么切換pcb的正反面?

2019-04-29 00:19:47

基于DSP的測試技術與傳統的測試技術相比,有哪些優勢?基本的混合信號測試技術包括哪些?采樣和重建在混合信號測試中的應用

2021-04-21 06:41:10

如何利用FPGA設計技術降低功耗?

2021-04-13 06:16:21

畫PCB怎樣,只顯示單獨的一層,其他層的線看不見?希望大神給予指到

2019-09-12 01:05:14

描述TIDA-00675可使用負載開關動態開啟/關閉負載,從而降低功耗。設計指南說明了開關頻率、占空比和放電電阻的使用如何影響功耗。特性通過動態開啟/關閉負載來降低功耗頻率、占空比和負載電流對功耗

2022-09-20 07:17:32

摘要 目前,為了降低功耗,越來越多的芯片支持動態電壓與頻率調節DVFS(Dynamic Voltage and Frequency Scaling)。本文列舉了基于軟件和硬件的DVFS實現,驗證了DVFS在降低功耗

2009-03-29 15:14:37 2482

2482

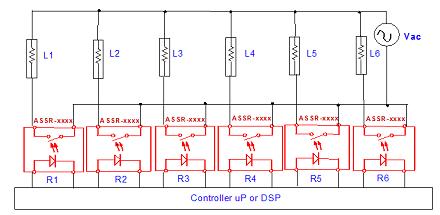

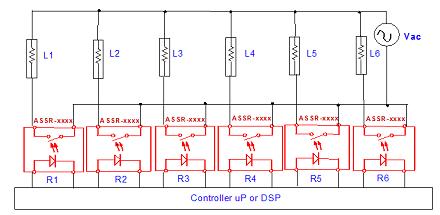

固態繼電器的動態功耗和設計考量

1.0 介紹

對于低電壓信號或低功率切換應用,具備MOSFET輸出的光學隔離固態繼電器(SSR, Solid State Relay)可以比傳統機電式繼

2010-02-22 09:14:58 2474

2474

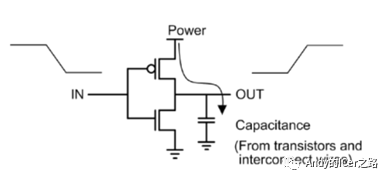

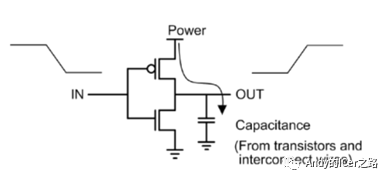

降低移動設計功耗的邏輯技術方法

本文將探討在混合電壓供電的移動設計中,混合電壓電平如何提高ICC電源電流及邏輯門如何降低功耗。當前的移

2010-04-15 15:00:46 666

666

設計人員總是在尋找減少不需要的功耗組件的方法,無論是通過以低功耗技術的方式設計設計,還是采用可以降低功耗的工藝。但是,其中一些解決方案的代價是性能,可靠性,芯片面積或其中的幾個。最終,人們必須在功率,性能和成本之間達成妥協。下面的文章旨在討論其中的一些技巧。這些技術分為建筑技術和基于過程的技術。

2019-08-09 14:32:55 14246

14246

電子發燒友網站提供《通過動態切換降低功耗的參考設計.zip》資料免費下載

2022-09-06 15:33:14 0

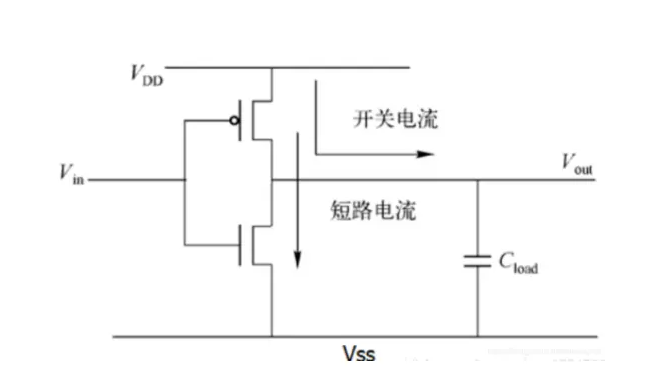

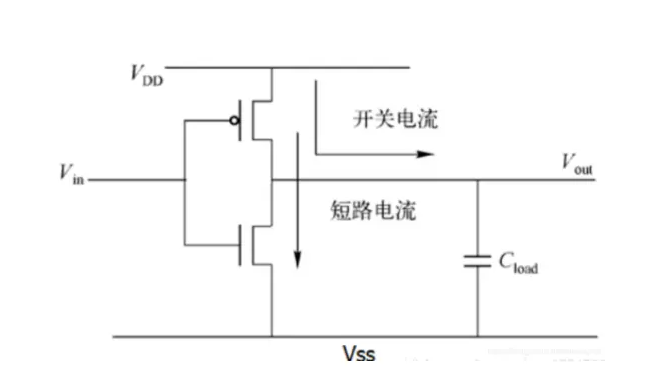

0 翻轉功耗是由充放電電容引起的動態功耗,其推導過程很簡單,但是這個最終的結果卻十分重要。

2023-06-05 17:36:26 2034

2034

CMOS器件是一種采用CMOS技術制造的電子器件,具有低功耗、耐電磁干擾、高噪聲免疫性等優點,被廣泛應用于現代電子領域。本文將介紹cmos動態功耗公式以及和cmos動態功耗有關的電路參數。

2023-07-21 15:55:55 2317

2317

。 優化軟件算法:通過優化軟件算法,減少處理器的計算量,從而降低功耗。 休眠模式:對于不需要時時采集數據的設備,采用休眠模式,降低功耗。 動態調整采樣率:根據需要采集數據的頻率來動態調整采樣率,降低功耗。 優化供

2023-10-11 09:29:00 511

511

電子發燒友App

電子發燒友App

評論