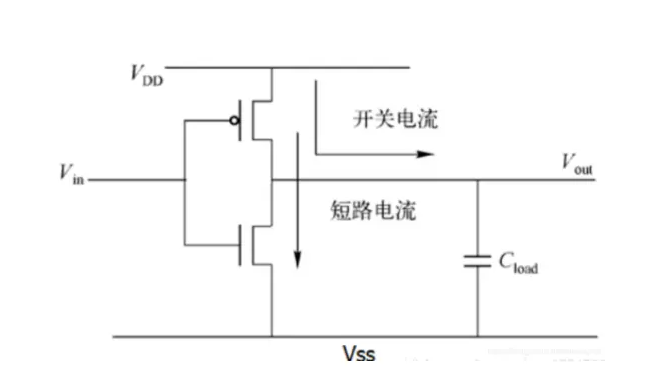

隨著行動裝置成為市場主流,以及不斷攀升的能源成本和環保意識的提高,功耗(power consumption)已成為設計人員最關心的議題。功耗大抵可分為兩部分,其一是靜態(static)或漏電(leakage)功耗,當元件處于待機狀態時該情況自然會產生;其二是動態功耗(dynamic power),指的是元件切換過程中所產生的功率消耗。就降低功耗而言,兩者都是設計上重要的議題;而這份報告主要是探討動態功耗及如何改善其相關的度量(metric)。

傳統設計中的另一層考量

過去數十年來,設計人員運用合成(synthesis)設計塬則進行設計,如此可產生同步時脈(synchronous clock-based)的架構。在這樣的設計方法下,所有的邏輯電路轉換由透過時脈網路分配的主時脈所支配。若最長的邏輯路徑(logic path)超過主時脈的週期時間,則設計人員必須設法減緩時脈,或者加快長路徑的速度。為了最有效地權衡兩者,設計人員會使用靜態時序分析工具,進行最長路徑的運算及邏輯電路的最佳化,直到他們達成所預定的時序頻率。

以上所述是當今設計所運用的基本方法論,它的效果不錯、能達成每個技術節點的速度優化,而且極為可靠。然而就當今的設計環境來說,其主要的缺點是它把面積(area)和功率列為第二和第叁考量順位,但以目前消費者對于更小、更快速且強調功能特色裝置的迫切需求而言,設計人員不能再把面積與功率視作次要的設計目標,而是必須審慎評估及改善這兩項度量,以滿足當今的設計要求。

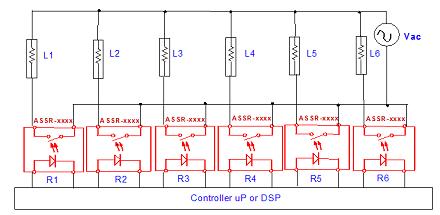

當我們在進行同步設計分析并將動態功耗納入考慮時,可以辨識出兩種造成過度功率耗損的塬因。其中之一是時脈分配(clock distribution),它能確保所有的邏輯電路與主時脈同步。整個時脈結構上的時脈偏移對于晶片的效能有直接的影響,因此必須設法將時脈延遲及偏移的發生降至最低。儘管上述架構允許設計人員提高時脈頻率(及效能),但它也會消耗掉20%到60%的晶片功率,且需要大量的半導體空間。換句話說,這種設計方法雖然效率高但成本也高,特別是在功率方面。

同步設計也意味著電路中的所有轉換會「聚集(bunch up)」在時脈邊緣。舉例來說,在每個有效時脈邊緣上,所有發生在邏輯路徑的轉換會同時被執行,而當條件順著組合邏輯鏈(combinatorial logic chain)被滿足后,這些轉換就會逐漸停止。若以圖示表示,該現象可用鋸齒波形來呈現。而大多數的動態功率就是在這樣的執行過程中被消耗掉的,直到路徑末端幾乎沒有功率被消耗為止。若是在最佳時序的狀態下,則最后的轉換應當在下一個時脈進行前就減弱。

就時序(timing)而言,該方法論的效果不錯,若能妥善分配週期中的轉換以及消除鋸齒波形,則在任何時間點所需的最大功率將會大幅降低,幅度約30%到50%左右。這是因為電源供應線不需要處理每個時脈周期(clock cycle)一開始產生的眾多元件切換所帶來的電流突波(power surge),也因此可以減少面積并降低功率的浪費。

有一個簡單但不切實際的解決方式是,建立一個帶有適當延遲的客製邏輯電路(custom logic)去達成每個輸出點所欲達到的功能,藉此妥善調整功率的分派。這個做法可以讓速度變得很快,有點類似讓單一印表機對上單一電腦,而不是透過區域網路讓多個使用者共享一臺印表機的資源。然而這樣的架構需要大量的面積、邏輯電路及功率才能恰當的運作。我們相信一定有其他更好的方式能達成時序、效能、功率及面積的目標,同時又能符合經測試且有效率的合成設計方法(methodology of synthesis-based design)。

提升省電效率的方法

時脈閘控(clock gating)是用來在同步設計環境中,達成較佳動態功耗效能的最常見技術。時脈閘控本身即是違反傳統的同步設計規則,而當今很多工具便是利用這樣的「漏洞(loophole)」成功地改善功耗的問題。利用時脈閘控技術,除非輸入至正反器(flip-flop)的資料遭到改變,否則正反器將不會接收到時脈訊號, 如此一來可以避免把功率浪費在正反器單元中,以及避免把功率用在受到閘控的任何時脈樹部分。因此,當前的設計工具大量利用時脈閘控達成大幅降低動態功耗的目的。

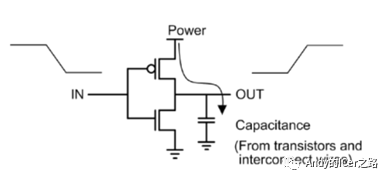

在任何復雜的邏輯錐(cone of logic)中,當路徑進一步到達邏輯錐區時,很多轉換便會被封鎖住,而無法透過時脈閘控來抑制。其中有些轉換可作為「資料閘控(data gating)」用,而這個時候便能識別出,那些在不影響電路輸出情況下進行轉換的邏輯電路。常見的例子像是在某些時間點未被使用的操作輸入,或是在週期中進行改變的記憶體讀取地址。平息這類型的轉換將大幅降低電路中耗費功率的轉換,同時對時序造成的影響也最小。進而使得該電路變得更省電。

將功耗降至最低的工具

為了進一步提升效率,設計人員必須在架構層級(architectural level)進行最新技術的運用。新思科技DesignWare minPower Components在各式環境中,都能盡可能地以耗用最低功率的方式運作。架構上來說,這些元件是在最省電的配置下被執行,它們用來執行各自的功能,同時將耗用功率但無產出的假性轉換的數量降至最低。而透過Design Compiler Ultra (DC Ultra)改善實作過程中的架構性選擇(區域時序及交換動作都可被納入考量),minPower Components可為所有運算環境提供最佳架構性解決方案。

此外,分析顯示,由于其大型的電路尺寸及頻繁的交換活動,資料路徑電路(datapath circuits )經常耗用大量的動態功率。而對于必須維持電源開啟一段時間的電路而言,這類的影響也就越顯著。為了降低這些電路的功耗,DesignWare minPower Components包含了一系列具有轉換機率成本的資料路徑架構。當使用DesignWare minPower Components IP及DC Ultra流程,它能讓資料路徑產生器計算每個架構及編碼決策的功率,進而讓DC Ultra產生可以平息交換活動的路徑資料架構、限制錯誤的產生及傳遞,以及利用較高比例的低漏元件資源。

DesignWare minPower Components亦附有利用轉換機率(transition probabilities)的功率模型,不論所提供的實際交換動作是使用者定義或是來自交換動作互換格式(Switching Activity Interchange Format,SAIF)中的模擬向量,DesignWare minPower Components都可根據交換的內容,進行資料路徑架構的最佳配置。它可以以最佳的方式重新排列資料路徑樹(datapath tree)及改變運算編碼,以便停止交換動作及錯誤的產生,進而減少功耗。

該高層級優化技術還可以協助設計人員根據個別設計的特性達到功率的節省。資料路徑架構可以讓設計達成友善的資料路徑閘控,且當資料無效時可讓設計人員關閉整個路徑資料區塊的交換。該路徑資料架構是依照可利用嵌入閘控邏輯進行配置的結構所設計,如此可以排除對于外部隔絕閘的需求,因為這類的需求經常會降低時序的特性。

另外,在現有的低功耗設計流程中如果採用DesignWare minPower Components也相當地簡明易懂。例如時脈閘道技術、低功率合成以及利用多層臨界電壓降低漏電等方式仍然可以搭配使用,以生產更省電的設計。

結論

在設計技術持續演進的過程中,動態功耗仍是低功耗設計的重要議題。任何晶片的功能都是透過邏輯電路的轉換來達成,而這些轉換會耗用掉功率。省電效率對當今復雜的晶片來說是如此重要,以致于設計人員必須不斷尋找新的方式,在耗費最小功耗的前提下達成最大的效益。傳統的同步設計方法論仍有運用的空間,但結合非同步設計、資料敏感度,及較高層級方式的混合式解決方案,也不失為一個好的折衷方式,而這類的解決方案有仍待設計人員的持續探索。

電子發燒友App

電子發燒友App

評論