EDA篇

本次硅谷之行的第三天,筆者又見(jiàn)到了老朋友,Mentor董事會(huì)主席兼CEO Walden C. Rhines(見(jiàn)圖1)。這次,有著數(shù)十年資深技術(shù)背景的Walden既沒(méi)有談具體EDA技術(shù),也沒(méi)有講市場(chǎng),而是回顧了EDA驗(yàn)證的歷史變遷。

圖1 Mentor董事局主席兼CEO Walden C. Rhines(右),副總裁兼設(shè)計(jì)驗(yàn)證技術(shù)部總經(jīng)理John Lenyo(左)

邁入驗(yàn)證3.0時(shí)代

在早期的中小規(guī)模(SSI/MSI)集成電路設(shè)計(jì)和驗(yàn)證中,基本靠設(shè)計(jì)師手工設(shè)計(jì)和布局,然后是架構(gòu)、測(cè)試、重復(fù)設(shè)計(jì),直至項(xiàng)目完成。

1973年4月12日,美國(guó)加州大學(xué)伯克利分校電子工程系電工實(shí)驗(yàn)室的L.W.Nagel和D.O.Pederson,開(kāi)發(fā)出了電路仿真軟件SPICE。借助這款軟件,設(shè)計(jì)師可快速可靠地驗(yàn)證電路設(shè)計(jì)并預(yù)測(cè)電路性能。

隨著10萬(wàn)門以上大型設(shè)計(jì)對(duì)仿真的需求,1982年,Mentor開(kāi)發(fā)出了基于IDEA工作站的QiuickSim數(shù)字電路仿真器。

Walden把這個(gè)時(shí)期稱為“驗(yàn)證0.0時(shí)代”。

此后,便進(jìn)入了寄存器傳輸級(jí)描述的“驗(yàn)證1.0時(shí)代”。這個(gè)時(shí)期的設(shè)計(jì)特點(diǎn)是,更加關(guān)注描述語(yǔ)言及性能提升。

代表性語(yǔ)言是VHDL。1981年,美國(guó)國(guó)防部提出了VHSIC語(yǔ)言。1983年,IBM、TI及Intermetrics獲得了相關(guān)開(kāi)發(fā)合同。1987年,VHDL被確定為IEEE1076標(biāo)準(zhǔn)語(yǔ)言。

1984年,GateWay設(shè)計(jì)自動(dòng)化公司的Phil Moorby創(chuàng)建了Verilog HDL語(yǔ)言。1989年,GateWay被Cadence***。1995年,Verilog成為IEEE1364標(biāo)準(zhǔn)語(yǔ)言。

另外,RTL加速仿真提升了硬件性能。

接著,芯片設(shè)計(jì)又進(jìn)入了更加關(guān)注方法學(xué)的測(cè)試平臺(tái)(testbench)自動(dòng)化“驗(yàn)證2.0時(shí)代”。2002年,SystemVerilog語(yǔ)言出現(xiàn)。

Walden稱,他曾在2004年設(shè)計(jì)自動(dòng)化大會(huì)(DAC)的CEO圓桌論壇上與新思(Synopsys)CEO Aart de Geus的激辯中,力挺SystemVerilog,并提出業(yè)界應(yīng)該創(chuàng)建一個(gè)SystemVerilog的設(shè)計(jì)環(huán)境。令他欣慰的是,同年,SystemVerilog被批準(zhǔn)為IEEE1800標(biāo)準(zhǔn)語(yǔ)言。

目前,在10多億美元的驗(yàn)證市場(chǎng)上,SystemVerilog已成為測(cè)試平臺(tái)主流驗(yàn)證語(yǔ)言,且遠(yuǎn)高于VHDL、System和C/C++等。

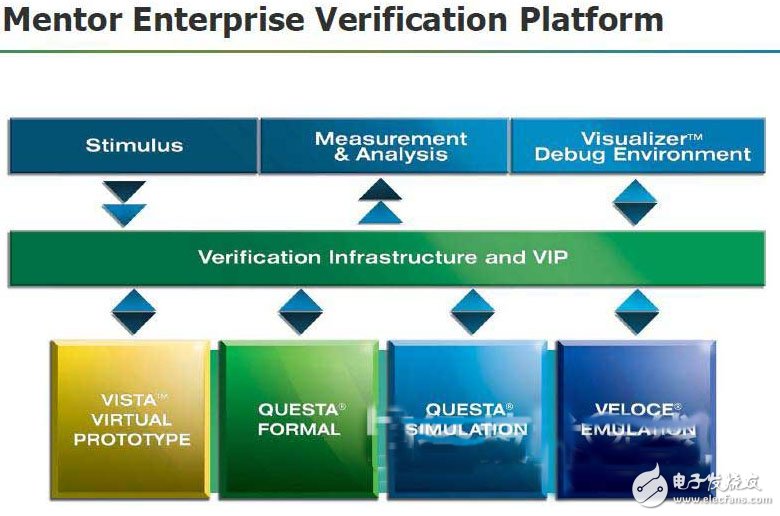

企業(yè)級(jí)驗(yàn)證平臺(tái)

Mentor副總裁兼設(shè)計(jì)驗(yàn)證技術(shù)部總經(jīng)理John Lenyo(見(jiàn)圖1)對(duì)2014年6月即將上市的企業(yè)驗(yàn)證平臺(tái)(EVP)進(jìn)行了詳細(xì)闡述。EVP結(jié)構(gòu)示意圖如圖2所示。

圖2 Mentor的企業(yè)級(jí)驗(yàn)證平臺(tái)(EVP)

該驗(yàn)證平臺(tái)包括:①仿真加速操作系統(tǒng)Veloce OS3、②統(tǒng)一的硬件調(diào)試環(huán)境Visualizer、③軟件調(diào)試器Codelink,④支持Questa和Veloce的驗(yàn)證IP。因此,可形成全球范圍的資源數(shù)據(jù)中心(見(jiàn)圖3)。

圖3 Mentor數(shù)據(jù)中心里的容納幾十臺(tái)Veloce仿真加速器的機(jī)柜

①Veloce OS3支持低功耗的UPF驗(yàn)證;SystemVerilog功能覆蓋率和基于斷言的驗(yàn)證;及SystemVerilog、UVM和C/C++測(cè)試平臺(tái)。具有高覆蓋率收斂流程,并進(jìn)行應(yīng)用程序軟件關(guān)鍵的SoC子系統(tǒng)的流片前性能分析。為了最大程度地復(fù)用驗(yàn)證平臺(tái),按照UVM/RTL標(biāo)準(zhǔn),為仿真和加速模式專門設(shè)計(jì)了驗(yàn)證IP。在保證功能的前提下,可比單獨(dú)仿真性能提高1000倍(見(jiàn)圖4)。

圖4 Veloce OS3可加速現(xiàn)有的仿真驗(yàn)證環(huán)境

可用虛擬環(huán)境取代實(shí)際硬件。PCIe、以太網(wǎng)和USB等標(biāo)準(zhǔn)接口,都可在工作站中實(shí)現(xiàn)虛擬化。

隨著復(fù)雜度更高的SoC設(shè)計(jì)項(xiàng)目的增加,例如,系統(tǒng)中含有多個(gè)嵌入式內(nèi)核、異構(gòu)處理器、復(fù)雜的系統(tǒng)內(nèi)部互連、存儲(chǔ)器共享、片上網(wǎng)絡(luò)及多級(jí)緩存,“芯片開(kāi)始驗(yàn)證轉(zhuǎn)向系統(tǒng)級(jí)驗(yàn)證,側(cè)重于軟硬件協(xié)同驗(yàn)證的設(shè)計(jì)終于邁入了‘驗(yàn)證3.0時(shí)代’”。 Walden指出。

隨著工藝節(jié)點(diǎn)的發(fā)展,嵌入式軟件工程師激增,16nm工藝時(shí)代是90nm時(shí)的17倍。同時(shí),處理器的工作頻率也達(dá)3GHz以上。

對(duì)于系統(tǒng)及驗(yàn)證,仿真更是必須。而驗(yàn)證的關(guān)鍵是軟硬件協(xié)同。仿真也需從設(shè)計(jì)師的實(shí)驗(yàn)室轉(zhuǎn)向數(shù)據(jù)中心。

Walden表示,驗(yàn)證3.0時(shí)代需要企業(yè)級(jí)的解決方案,包括調(diào)試、驗(yàn)證IP、用戶接口、測(cè)試平臺(tái)仿真、斷言及覆蓋。

Veloce OS3 VirtuaLAB外圍設(shè)備是立即可重配的,可支持世界各地的多個(gè)項(xiàng)目團(tuán)隊(duì)。OS3企業(yè)服務(wù)器能夠有效地管理全球硬件仿真加速器資源,并將其導(dǎo)入商業(yè)隊(duì)列管理器中,形成單一的高容量實(shí)體。企業(yè)服務(wù)器決定著每項(xiàng)工作的優(yōu)先順序,迅速切換優(yōu)先項(xiàng)目。

②有了SoC設(shè)計(jì)軟件,設(shè)計(jì)團(tuán)隊(duì)就可將大部分驗(yàn)證時(shí)間用于調(diào)試。因此,提高從模塊到系統(tǒng)的調(diào)試效率十分重要。Visualizer調(diào)試器、仿真和硬件加速器具備處理現(xiàn)有最大SoC的容量和性能。Visualizer調(diào)試器提供了高效的RTL、門級(jí)和測(cè)試平臺(tái)的調(diào)試,包括自動(dòng)追蹤以快速精確定位出錯(cuò)誤的根本原因,協(xié)議和事務(wù)級(jí)調(diào)試,自帶的UVM和SystemVerilog基于類的調(diào)試功能,及低功耗UPF調(diào)試。仿真和硬件加速的交互模式和后仿真模式也具有上述功能。

③在具備啟動(dòng)OS的功能后,SoC簽發(fā)(signoff)解決方案才得以完善。軟件調(diào)試操作系統(tǒng)時(shí),往往需要較多的思考時(shí)間,而硬件加速器處于空閑狀態(tài)。OS3將思考時(shí)間轉(zhuǎn)移到Codelink工具上,Codelink工具最多可同時(shí)支持10個(gè)設(shè)計(jì)師進(jìn)行JTAG調(diào)試,且回放軟件執(zhí)行速度為100MHz。借助OS3,硬件加速器可以全速執(zhí)行各任務(wù),而軟件進(jìn)行離線調(diào)試。上述功能可在設(shè)計(jì)周期中最大程度地提高調(diào)試效率,并盡可能早地啟動(dòng)OS。

④驗(yàn)證IP支持Questa和Veloce,具有共同的仿真驗(yàn)證和測(cè)試平臺(tái)特性,軟件可移植,測(cè)試環(huán)境可重用(見(jiàn)圖5)。

圖5 驗(yàn)證IP具有測(cè)試平臺(tái)可移植性

許多 SoC項(xiàng)目的驗(yàn)證數(shù)據(jù)有多個(gè)來(lái)源,需對(duì)驗(yàn)證數(shù)據(jù)合并與綜合分析,以評(píng)估實(shí)際項(xiàng)目的完成情況。Veloce OS3 和Questa 10.3可將所有斷言、覆蓋率和運(yùn)行時(shí)間數(shù)據(jù),包括硬件仿真、形式驗(yàn)證、仿真、混合信號(hào)和低功耗等,寫入共同數(shù)據(jù)庫(kù)。借助共同數(shù)據(jù)庫(kù)、Questa驗(yàn)證管理工具和測(cè)試計(jì)劃,驗(yàn)證小組能夠立即查看覆蓋率情況,準(zhǔn)確查出無(wú)效測(cè)試,縮短數(shù)據(jù)合并時(shí)間,提高回歸測(cè)試的吞吐率,減少調(diào)試時(shí)間,從總體上提高產(chǎn)品質(zhì)量和生產(chǎn)率。

EVP 統(tǒng)一覆蓋數(shù)據(jù)庫(kù) (UCDB)支持統(tǒng)一覆蓋互通性標(biāo)準(zhǔn)(UCIS),在了解其它驗(yàn)證引擎已取得的覆蓋率的情況下,優(yōu)化下載到硬件加速器的邏輯的覆蓋率,縮短編譯時(shí)間,節(jié)約硬件仿真資源,創(chuàng)建更智能的覆蓋率收斂流程。

最后,Lenyo總結(jié)指出,實(shí)際上,企業(yè)驗(yàn)證平臺(tái)就是把虛擬原型、架構(gòu)分析和軟硬件加速仿真結(jié)合在一起,使從最初設(shè)計(jì)創(chuàng)意、硅片制造到成品的整個(gè)驗(yàn)證過(guò)程均從基本驗(yàn)證引擎中提取出來(lái)。

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論