筆者再次來到美國加州硅谷,開始為期一周的***總部技術探秘之旅。5天內共采訪了Maxim(美信)、Analogix(硅谷數模)、Arteris、Lattice(萊迪斯)、Mentor Graphics(明導)、Silego、Silicon Image和GEO等8家半導體廠商,并聆聽了一場Gartner關于物聯網市場和技術的演講。

首先還是看看筆者每次來硅谷時用以判斷半導體行業發展狀態的“汽車數量指數”晴雨表吧。所到幾家廠商總部的停車場內,基本都停滿了員工們的各種座駕。之前在國內從多種渠道了解到,美國經濟已經恢復上升趨勢,半導體行業景氣指數也在不斷攀升。這次親眼驗證了上述說法。

下面將分篇介紹本次硅谷技術探秘的所見所聞

汽車電子篇

老牌Maxim模數全能

第一天采訪的Maxim和最后一天采訪的GEO都有汽車電子業務。不同的是,Maxim是一家有著30年歷史的老牌半導體廠商,年營收達24億美元,每年研發資金約5億美元。汽車電子業務主要是電源管理、ADAS(高級駕駛輔助系統)和信息娛樂系統等的模擬、混合信號解決方案。而GEO只有5歲,汽車電子主要關注幾何圖形處理和視頻處理。由于是初創型公司,所以年收入沒有對外公布,不過,據了解,這幾年的研發投入共約1億美元。巧的是,兩家公司還有些淵源。2012年,剛成立3年的GEO***了Maxim的數字視頻IC部門。

Maxim汽車電子解決方案部門執行總監Kent Robinett(見圖1)指出,未來5年內,車載CD播放器將會落伍,駕乘者的車內信息娛樂體驗將會趕上移動互聯終端那樣的體驗;駕駛輔助功能將成為所有乘用車的標配,這有助于把交通事故率減少50%。此外,美國交通管理部門要求,2018年,乘用車必須安裝倒車影像監控系統;LED車燈將繼續實現品牌差異化,這對環境和安全有著積極意義。

圖1 Maxim汽車電子解決方案部門管理團隊成員。執行總監Kent Robinett(左二)、執行總監Jon Horner(左一)、總監Farhad Farahbakhshian(右一)、高級業務經理Ben Landen(右二)。

對于汽車信息娛樂系統,1997年之前第一代的成本只有幾美元,1998~2006年第二代的成本曾飆升到了上千美元,2007~2010年第三代的成本回落到了幾百美元。隨著顯示、射頻前端、ECU、3G/4G無線通信及云計算的發展,2011年之后第四代汽車信息娛樂系統的成本將進一步下降到幾十美元甚至更低。

另據Strategy Analytics對英美車主的一項調查結果,消費者非常渴望擁有車上裝有ADAS系統,不過,他們認為ADAS目前的價格太高而不愿購買。預計2017年,各種不同類型ADAS產品的市場規模將增長到近9000萬套。現在面臨的技術挑戰是,要能在低成本線纜上無壓縮地傳送百萬像素的數據,而且有很好的EMC性能。

Robinett透露,針對高清中控和后排顯示,及ADAS等車載信息娛樂系統,他所領導的汽車電子方案部門最新推出了3.12Gbps多媒體串行鏈路(GMSL)SerDes芯片組。其特點是,可使屏蔽雙絞線和同軸電纜兼容,并降低同軸電纜50%的成本和重量;線纜傳輸距離為15m;采用專利的全雙工串行傳輸架構;片上擴頻時鐘,可降低EMI,因而不需要外部擴頻時鐘。

對車載顯示器、LED背光燈及抬頭顯示系統(HUD),帶高壓DC/DC控制器和電池分離功能的四通道LED驅動器MAX16813,最多可驅動4串高亮度LED燈。其特點是,減少了EMI噪聲,拓寬了動態范圍,同時,在關斷時,可使電池漏電流降到最低。

汽車儀表盤和信息娛樂系統的電源管理方面,含有3個大電流DC/DC轉換器的MAX16993,可節省50%以上的電路板面積,并減少AM頻段噪聲,降低EMI輻射。

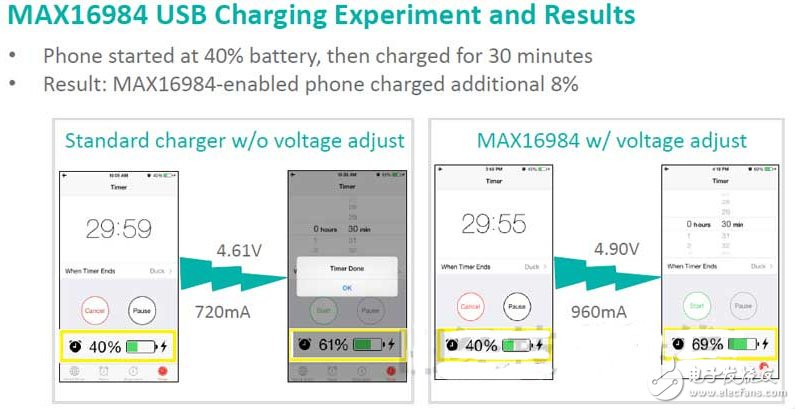

對于喜歡在車上用USB為智能手機和平板電腦等移動終端充電的人們,DC/DC轉換器MAX16984可用汽車電池進行安全可靠的充電。在移動終端剩余電量40%的情況下,充電30分鐘,MAX16984方案比市場現有的標準方案可多充8%(見圖2)。據了解,目前針對的是USB2.0,正在開發支持USB3.0的方案。

圖2 采用MAX16984的充電方案與市場現有標準方案的比較

新兵GEO專攻視頻處理

筆者本次采訪的其他廠商都有自己的一座或幾座辦公樓,其中Lattice的辦公樓旁還有一個長條狀、蜿蜒曲折的水池,環境甚好。

而GEO由于是初創型公司,與那些財大氣粗的豪門或準豪門不能攀比,現在過日子還得算計著花,錢要用到研發的刀刃上,所以只能暫時蝸居在合用辦公樓的半層。因為面積小,不帶大會議室,在演講和接受采訪時,也是在臨時租的公用會議室里。不過,這并沒有妨礙它擁有世界級的獨創技術。

GEO董事長兼CEO Paul M.Russo(見圖3)表示:“視頻所在之處就有我們的機會。”據他介紹,公司現有2個芯片平臺:不帶CODEC的eWarp,適于攝像、抬頭顯示系統和投影系統應用;eWarp+CODEC的CloudGEO,適于云、物聯網、可穿戴設備上的攝像機。

圖3 GEO董事長兼CEO Paul M.Russo

Russo透露,2款40nm工藝的芯片已出樣片,并將在2014年3季度量產。

GEO現有的50個客戶中,不乏像索尼、夏普、松下、日立、飛利浦、博世、霍尼韋爾等全球知名品牌,中國的海信也位列其中。據悉,比亞迪很可能成為其在汽車領域的客戶。目前,云攝像機、安防監控、智能電視和投影儀客戶的產品都已上市,汽車類客戶的產品將在2014年稍晚時間上市。

市場研究機構Techno Systems Reserch的報告顯示,未來5年,每輛汽車中可能會有多達8個攝像頭。2014年,車用攝像頭和抬頭顯示芯片的市場規模約為3億美元,2018年將達到9.4億美元。

該報告認為,美國高速公路安全管理局(NHTSA)和歐洲新車碰撞測試(EuroNCAP)的汽車安全法規將推動車用攝像頭市場快速增長。預計2014年,車用攝像頭的市場規模約為5290萬個;2018年,總數約1.077億個。這期間的年平均復合增長率約為24.4%。

2014年,所有本田和Acura車型將全部安裝攝像頭單元。日本松下、索尼、韓國現代摩比斯(Hyundai Mobis)和加拿大麥格納(Magna)4家一級供應商在車用攝像頭市場占了近半壁江山,其中松下占全部市場的1/5。

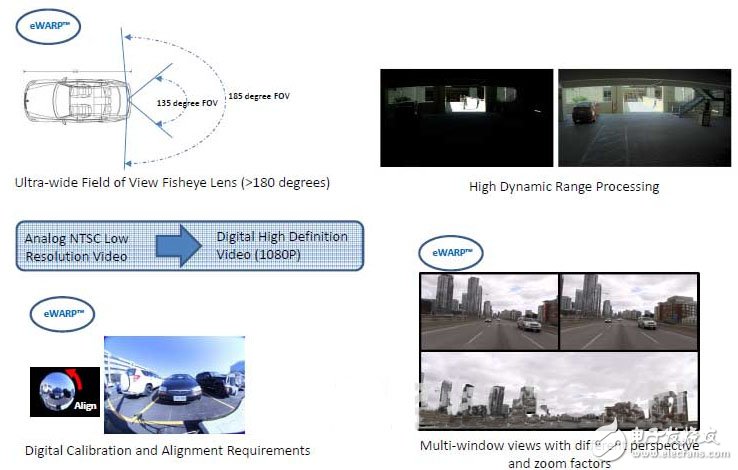

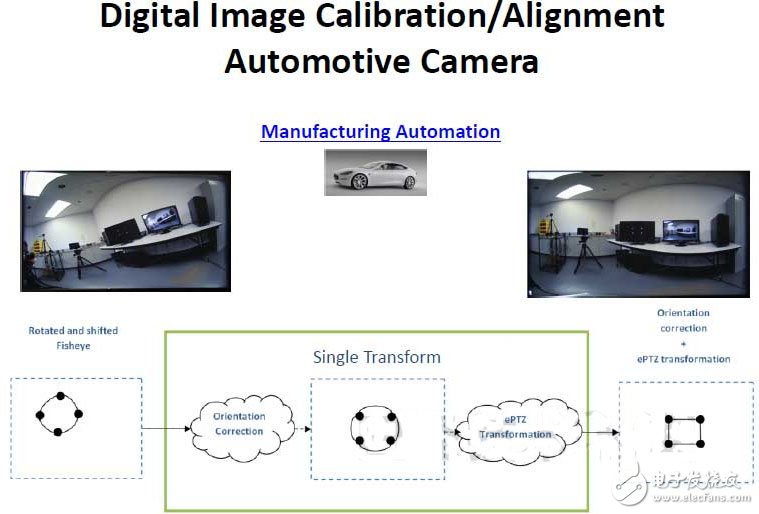

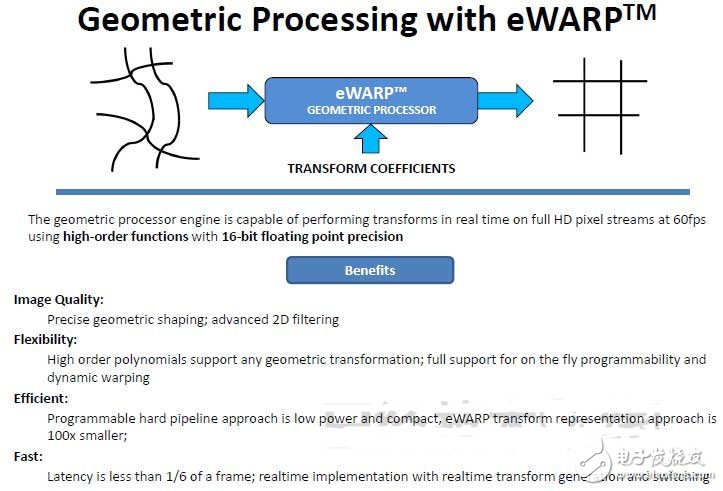

GEO的可編程eWarp處理器平臺支持任意尺寸圖形像素實時變換,可起到多個獨立幾何校正的作用,如鏡頭畸變校正,全景拼合圖像,取代物理調節的校準,及ePTZ的實時潘傾斜和變焦(pan tilt and zoom)。還有,對于180°以上的超廣角魚眼鏡頭,GEO的無內容損耗(Zero Content Loss)1080p全高清60fps視頻畸變校正專利技術,可進行實時圖像變換計算。上述技術分別如圖4~6所示。

圖4 GEO可編程eWarp處理器在汽車攝像頭系統中的應用(1)

圖5 GEO可編程eWarp處理器在汽車攝像頭系統中的應用(2)

圖6 GEO可編程eWarp處理器在汽車攝像頭系統中的應用(3)

目前汽車中的前后左右4個VGA攝像頭系統,可被一塊eWarp處理器芯片的圖像變換功能取代(見圖7)。例如,可用于自動泊車系統。該技術最開始被用于高端SUV車型,現在已逐步進入轎車中。

圖7 采用一塊eWarp處理器芯片的全景俯視系統

抬頭顯示技術最初用在美國和法國的軍用和民航飛機上。后來,通用汽車擁有了該技術在汽車上的專利,目前,專利已經公開。1988年,該技術首次選裝在通用汽車的Cutlass Supreme(超級短劍)車型上。

GEO和Techno Systems Reserch預計,2014年,抬頭顯示系統的市場規模約為350萬套。2016年將出現快速增長,約860萬套。2018年將上升到1510萬套。這期間的年平均復合增長率約為22.7%。

2014年,寶馬將在大部分車型中配置抬頭顯示系統。通用汽車也將擴大裝配的車型種類。奔馳將調整市場戰略,2014年秋季,在S和C級車型中配置抬頭顯示系統。日本精機(Nippon Seiki)、矢崎(Yazaki)、美國江森自控(Johnson Controls)、德國大陸(Continental)和日本電裝(Denso)分別占據了抬頭顯示系統傳統一級供應商的前五位。由于需求大,市場前景極為看好,松下、博世和現代摩比斯也正在擠入一級供應商陣營。

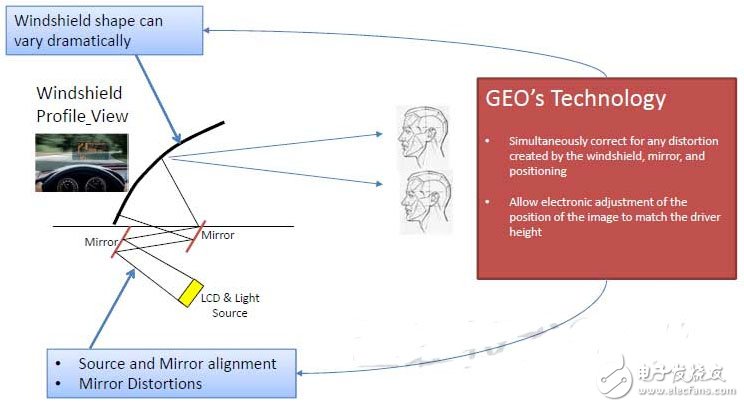

抬頭顯示系統目前面臨的挑戰包括:成本非常高,每套約1200~1500美元,這限制了它的市場普及度,因此只能用在部分高檔汽車里。用于投影顯示的前風擋玻璃較特殊,這使抬頭顯示系統的成本又增加了上百美元。此外,高清顯示和投影面積的擴大使圖像畸變問題更加凸顯。

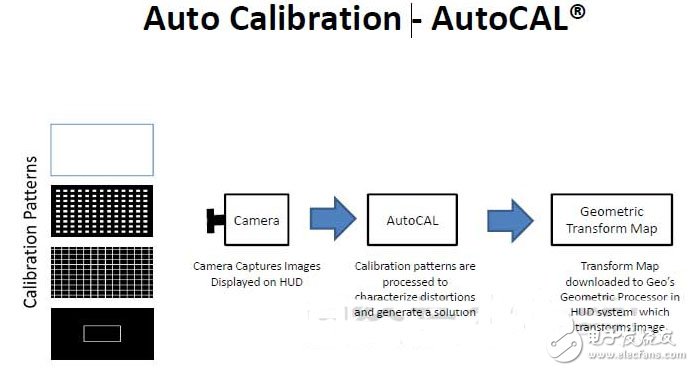

前面提到的GEO可編程eWarp處理器和視頻畸變校正專利技術,能同時校正風擋玻璃和短距光學微投影器產生的各種圖形畸變。還可以電子調節風擋上的圖像位置,這樣就不會因為駕駛員的身高而影響水平視角。如圖8~10所示。

圖8 GEO的自動校準技術

圖9 可編程eWarp處理器的幾何處理

圖10 可編程eWarp處理器和視頻畸變校正專利技術,能同時校正風擋玻璃和短距光學微投影器產生的各種圖形畸變,不會因為駕駛員的身高而影響水平視角。

另外,針對云、物聯網、可穿戴設備上的攝像機,GEO的GC6500(Raptor2)解決方案可提供eWarp實時像素處理引擎;支持最多8個獨立視頻流的編解碼,每個感興趣區域(ROI)都是獨立的;高動態范圍影像信號處理器(ISP),壓縮與視頻處理流水線等,及硬件參考設計和軟件架構。

同時,GC6500和GW3xx方案均支持180°和360°魚眼鏡頭;可編程eWarp引擎支持多視角流,畫中畫,多個鏡頭的影像合成;單獨流的獨立視角等。優勢是,消費者或用戶只用一個攝像頭即可,而沒必要再用多個攝像頭。

移動高清連接篇

MHL廣泛的生態系統

MHL技術標準由諾基亞、三星、Silicon Image、索尼和東芝,于2010年4月發起制定。主要面向小屏移動終端與大屏高清顯示設備之間的連接,如智能手機、平板電腦、數字電視等消費電子產品及PC。

現在采用MHL技術的產品市場規模約5億臺。全球前5個智能手機品牌中,有4家采用了MHL標準;前10家數字電視制造商中,有9家有4家采用了MHL標準。該陣營的廠商及成員近200個,如三星、索尼、東芝、夏普、聯想、海爾、海信、TCL、創維、HTC、***、中興、小米、魅族等。此外,還有現代、JVC-Kenwood、先鋒等汽車配件廠商。

圖1 Silicon Image業務開發高級總監兼首席宣傳官(Chief Evangelist)Jim Chase

Silicon Image業務開發高級總監兼首席宣傳官(Chief Evangelist)Jim Chase(見圖1)表示,2014年,采用MHL技術的智能手機、PC顯示器和數字電視的市場規模分別為22%、25%和28%,預計數字電視的這一比例將在2014年增加到40%以上。

除了中高端市場,面向新興市場的低端產品也在MHL的版圖之內。例如,一套采用MHL收發器的智能手機和筆記本電腦的套餐價在300美元左右(見圖2)。

圖2 采用MHL收發器的智能手機和筆記本電腦的套餐價在300美元左右

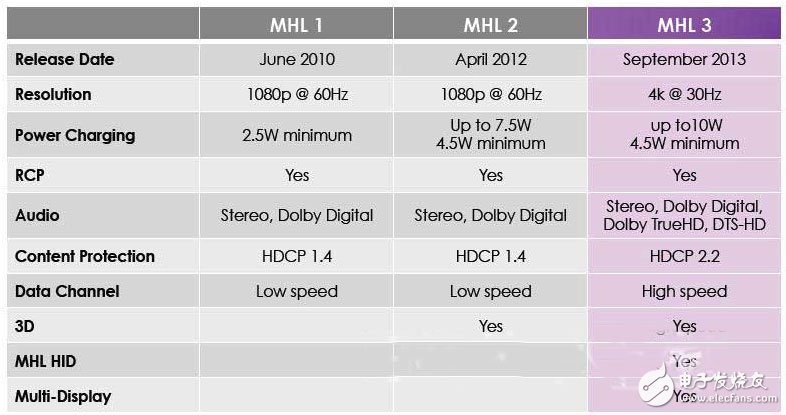

針對4K超高清顯示的布局也進行的如火如荼。2013年發布的MHL3.0版本可支持4K超高清顯示和高速數據傳輸。多屏顯示與移動設備充電可同時進行,充電功率在4.5W~10W(見圖3)。

圖3 MHL3.0標準特性

目前了解到的行業情況是,Simplay Labs已經制定了設備之間安全傳輸4K超高清內容的認證計劃。相關廠商提交的設備需要通過4K視頻、多信道音頻和HDCP 2.2鏈路保護支持及增強的互操作性測試。

NETFLIX已于2014年1月開始提供4K超高清視頻內容,索尼、YouTube、MGo也將在年內適當時間提供4K內容。

同時,高通、三星和nVidia的應用處理器,及三星、諾基亞和索尼等智能手機已為4K準備就緒。

采用MHL3.0、符合內容保護協議HDCP 2.2的三星智能電視,索尼智能手機和智能電視也正在迎接4K時代的到來。

Silicon Image為MHL 3.0、4K超高清生態系統開發的產品包括發射器,及MHL3.0到HDMI2.0的橋片等。

人無我有的60GHz無線高清連接

對于60GHz無線高清連接,Silicon Image同時是WirelessHD和WiGig標準組織的成員。

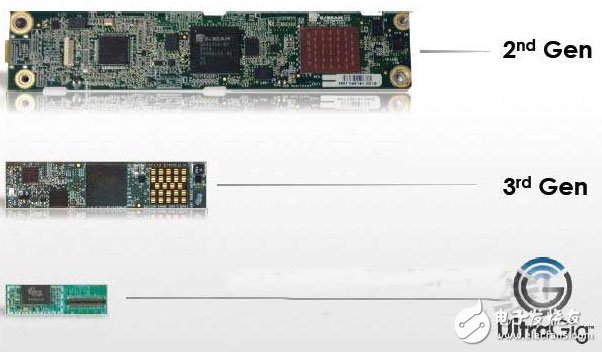

該公司負責標準業務工作的高級總監Rob Tobias表示,60GHz WirelessHD連接技術可把移動終端上的全高清視頻內容幾乎沒有延遲地傳輸到大屏上觀看(見圖4),并實現了大小屏的互動。智能天線確保了傳輸的穩定性,可與有線電纜傳輸的質量媲美。頻譜帶寬比WiFi高10~100倍,也不存在WiFi方案面臨的干擾問題。

圖4 60GHz WirelessHD連接技術可把移動終端上的全高清視頻內容幾乎沒有延遲地傳輸到大屏上觀看。

目前,集成了基帶、射頻和天線的單芯片UltraGig6400發射器的PCB面積為10mmx10mm,比第二代方案減小了10倍以上(見圖5)。UltraGig6400既可嵌入在智能手機和平板電腦里,也可作為外設插入。

圖5 60GHz無線高清(WirelessHD)連接方案的PCB改進比較

在高速數據傳輸方面,WiGig技術可作為WirelessHD的有力補充。

此外,Silicon Image面向4G/LTE小蜂窩無線回傳市場,開發了單芯片CMOS工藝的波束導向型60GHz射頻收發器。第三代60GHz射頻波束導向技術簡化了天線設計和安裝。工程樣本和評估板將于2014年第二季度提供。

硅谷數模圖謀8K

針對MHL的競爭,硅谷數模營銷副總裁Andre Bouwer(見圖6)稱,基于DisplayPort標準的SlimPort收發器,同樣可將智能手機、平板電腦和筆記本電腦等移動終端,與電視、監視器、投影儀等大屏顯示設備連接。(詳見《2013年暮春硅谷紀行(五))

圖6 硅谷數模營銷副總裁Andre Bouwe

他還表示,SlimPort4K產品也支持4K超高清、多屏幕、影音和USB數據及企業安全應用。支持音視頻和數據傳輸的SlimPort Pro版本(見圖7)正在開發中,準備提交給視頻電子標準協會(VESA)。

圖7 支持音視頻和數據傳輸的SlimPort Pro框圖和特性

用SlimPort給移動終端進行快速充電時的功率最高為9W。隨著采用SlimPort的移動終端及附件支持高通快速充電QC2.0技術,2014年,充電功率將提升至18W。

目前,LG、谷歌、富士通等原有合作伙伴已開發出采用SlimPort功能的新移動終端,而且,惠普和中興努比亞也加入了該陣營。例如,努比亞智能手機采用了SlimPort 4K解決方案,支持4K超高清內容。

同時,硅谷數模與瑞芯微合作開發了適于主流智能手機和平板電腦的基于SlimPort的參考設計,以進一步擴大SlimPort生態系統。

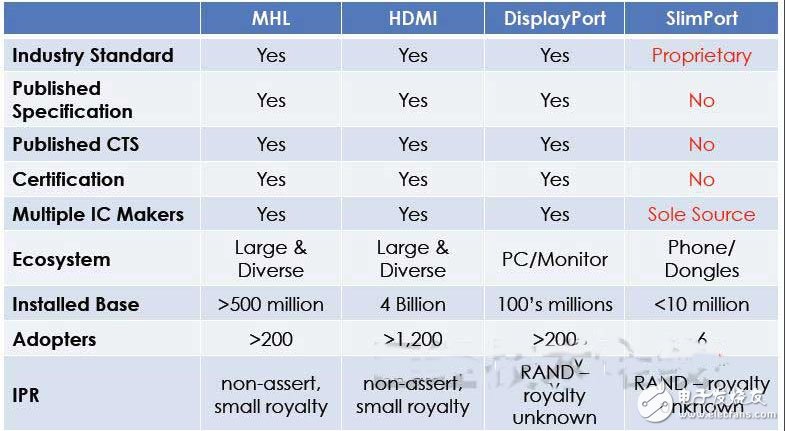

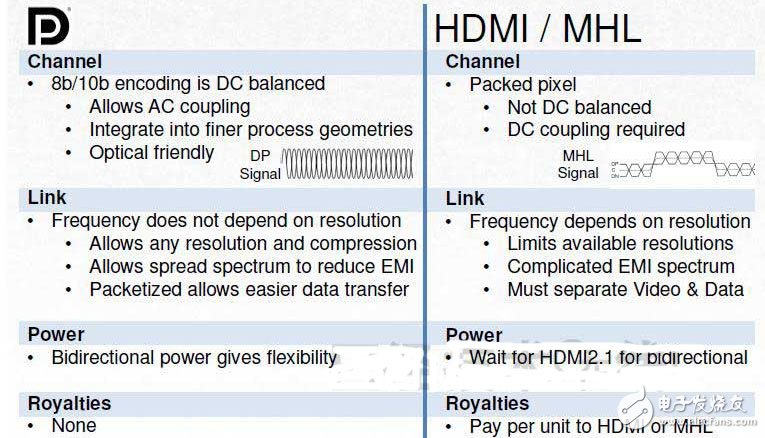

尺有所短寸有所長

至于MHL與SlimPort孰優孰劣,兩個對手給出了各自的評價(見表1、表2和圖10)。由于技術開發和市場一直在不斷變化,其中的某些性能對比和數據與現在的實際情況肯定會有偏差。例如,SlimPort的4K方案已經符合內容保護協議HDCP 2.2等。這些圖表比較僅供讀者們參考。

表1 MHL、HDMI、DisplayPort及SlimPort的標準比較(Silicon Image提供)

表2 MHL、HDMI與SlimPort的性能參數比較(Silicon Image提供)

圖10 DisplayPort與HDMI和MHL的技術特點比較(硅谷數模提供)

正所謂:尺有所短寸有所長。從上面的標準與技術比較,還不好說誰會笑到最后。終端開發商也需要根據自身能力、市場需求、整體設計難易和總成本來考慮應該采用哪種技術。

研究機構Display Search預計,2014年,中國4K電視市場規模約為1000萬臺,是全球其他地區總量的3倍。由于目前市場上主要的移動超高清連接技術就是MHL和SlimPort,所以,Silicon Image和硅谷數模勢必會為此展開激烈的搏殺。

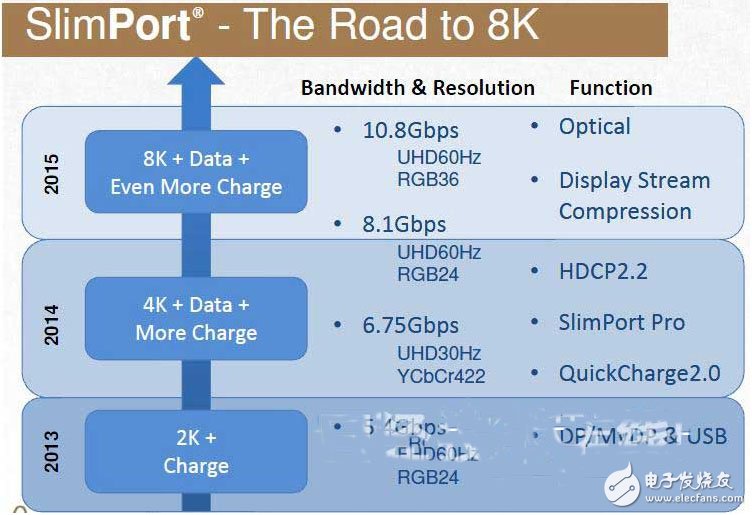

不過,由于4K的生態系統比對手弱,硅谷數模在繼續鞏固4K“籬笆”的同時,已開始覬覦8K市場。Bouwer特別指出:“不要說8K離我們還很遠,其實消費者已對4K超高清非常感興趣,他們對8K也會是同樣的態度。”

SlimPort的8K技術路線圖如圖8所示。與之前版本的DisplayPort標準相比,將要公布的DisplayPort1.3版本增加了HBR3,即傳輸速率為 8.1Gbps,可以支持DSC(Display Stream Compression)標準的60fps8K×4K視頻。DSC由VESA在2014年3月剛公布。

圖8 SlimPort的8K技術路線圖

DisplayPort1.3可在無壓縮情況下實現60fps8K×4K視頻傳輸,而SlimPort目前在壓縮情況下實現了30fps8K×4K的視頻傳輸(見圖9)。

圖9 DisplayPort1.3與SlimPort在壓縮和未壓縮情況下實現8K視頻傳輸的技術參數對比

?

可編程、可配置與IP篇

ECP5“打破陳規” 挑戰FPGA巨頭

在FPGA領域,與賽靈思(Xilinx)和Altera這兩個追求極致密度、超高傳輸速率、巨量晶體管數、最新工藝技術的巨頭不同,Lattice(萊迪思)走的是低成本、低功耗和小形狀因數之路。

Lattice總裁兼CEO Darin Billerbeck形容自身優勢時,用了快速和敏捷(Agility)這兩個詞,目的就是使用戶爭取到足夠快的上市時間。

他特別提到了兩個“最”產品。一個是號稱全球最小FPGA的iCE40,價格不到50美分,功耗最低25μW,1.4x1.48mmBGA封裝。

另一個是面向視頻安全監控、人機接口和移動終端的MachXO3,其每個I/O接口的成本不到1美分,2.5x2.5和3.8x3.8mm2的WLCS封裝。

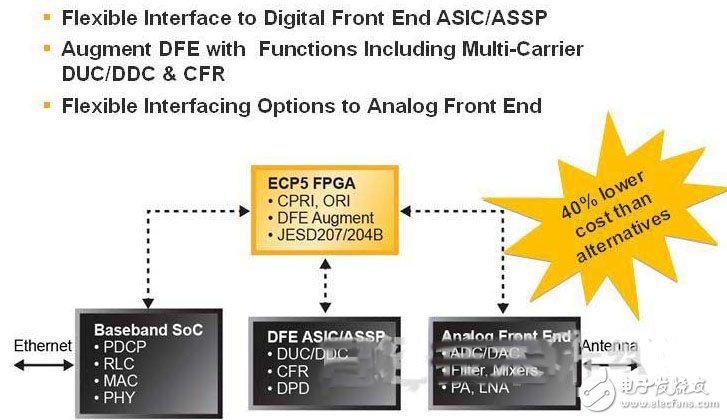

Lattice方面表示,除了上面差異化技術外,將以最新開發出的ECP5 FPGA系列,在小型蜂窩網絡、微型服務器、寬帶接入、工業視頻等大批量應用中,向兩大巨頭的中低端產品發起挑戰。

一段時期以來,賽靈思和Altera一直宣稱要用FPGA取代ASIC和ASSP。而Lattice則表示要讓ECP5在10萬LUT以下的設計中,成為ASIC和ASSP的輔助設計伙伴,以彌補ASIC的成本問題和ASSP不夠靈活的缺陷。

Darin Billerbeck稱,ECP5系列在成本、功耗和密度3個方面“打破了陳規”:

①2.5萬~8.5萬LUT在提高提高設計靈活性的同時,比市場上其他競爭產品的成本最多降低了40%。在小型蜂窩基站中的應用如圖1所示。

?

圖1 ECP5系列在小型蜂窩基站中作為ASIC和ASSP的輔助設計

②使用單通道3.25Gpbs SERDES,即一路PCIe時,最低功耗約為0.25W(見圖2)。若采用4路PCIe,功耗也不到0.5W。靜態功耗在64~78mW。在150MHz典型應用中的功耗,比競爭產品最多降低30%。

圖2 ECP5系列在安防監控攝像機方案中,使用單通道3.25Gpbs SERDES,即一路PCIe時,功耗約0.25W。

在現場演示中,用Diamond軟件工具測得8.5萬LUT設計的典型功耗約315mW;2.5萬LUT時為264mW。

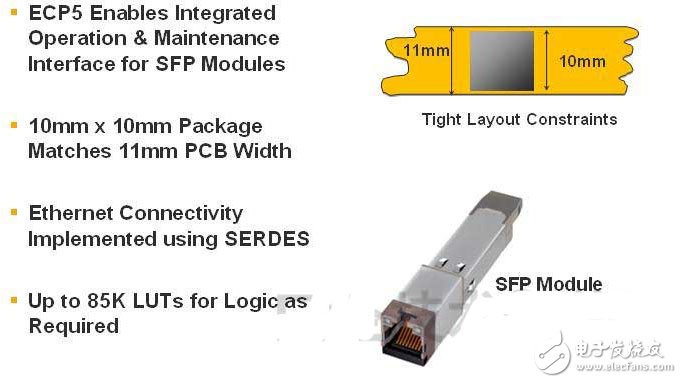

③8.5萬LUT和SERDES封裝在10x10mm2BGA內(見圖3),功能密度,即每平方毫米的LUT數量,比競爭產品高2倍以上。40nm工藝的ECP5系列比競爭產品28nm工藝的芯片尺寸還小。

圖3 ECP5系列采用10x10mm2BGA封裝,適于寬帶接入設備的智能小型可插拔(SFP)收發器方案。

據悉,ECP5預計將于2014年8月上市,并在2016年進入28nm工藝。

另外,市場方面,目前亞太地區營收占Lattice全球的60%,其中,中國占亞太區的70%。

神秘又熟悉的IP商

本次硅谷之旅第二天采訪的Arteris,是一家網絡芯片(Network-on-Chip)互連IP和工具供應商。盡管已有10多年的歷史了,但是它并不像處理器IP商ARM、MIPS、Tensilica、CEVA或Cadence、Synopsys那樣有很高的知名度,因而對于大多數電子工程師可能顯得有些神秘。

不過在半導體設計界,三星、高通、TI、飛思卡爾、ST、瑞薩電子、東芝和Altera等大牌都是Arteris的用戶。而且,中國大陸半導體設計三劍客海思、展訊、銳迪科,及全志科技、瑞芯微、珠海炬力和虹晶科技等不少公司,也采用了Arteris的FlexNoC互連IP進行SoC設計。據IHS iSuppli的調查報告,中國大陸多數半導體公司都得到了FlexNoC互連IP的授權。

最近,***創意電子(GUC)也得到了FlexNoC互連IP的授權,用于16nm移動設備應用處理器SoC IP驗證平臺的設計。

對于Arteris這樣既神秘又熟悉的廠商,在介紹其獨特技術之前,筆者覺得有必要對各位看官先普及一下它的歷史。

Arteris在2003年由3位法國人創立,總部設在巴黎。次年收到第一筆風險投資。2005年,現任董事長、總裁兼CEO K. Charlie Janac加盟,擔任CEO一職。2006年,第一個互連IP產品NoCSolution問世,并馬上就拿到了100萬美元的授權許可收入。

2007年,在得到由Synopsys領頭的新一輪投資后,把公司總部從巴黎搬到了硅谷。同年,TI的OMAP4應用處理器采用了NoCSolution的IP。2009年,第二代技術FlexNoC上市。隨后,得到了高通風險投資(歐洲)、ARM、日本Innotech等的第三輪投資。2010年,與三星和高通合作推出FlexLLI Interchip Link IP技術。

2011年,即公司成立的第8年,才開始盈利。2012年,全球60%的移動設計都采用了FlexNoC互連IP。2013年,在智能手機市場收獲頗豐。同年底,被高通以獨特的交易方式***了IP和工程團隊。2014年,Arteris宣布雇傭新的工程領導團隊。

下面就來看看Arteris的FlexNoC互連IP的獨到之處。

從事芯片設計的工程師都知道,高效的互連是SoC盈利的關鍵。同時,在競爭激烈的市場上,靈活的拓撲架構對產品差異化非常重要。

Arteris營銷副總裁Kurt Shuler幽默地表示:“Arteris is Switzerland。”對這句話,不只是筆者,就連一位來自歐洲的資深媒體同行也大惑不解:“你們不是美國公司嗎?怎么又是瑞士的了?”

Shuler解釋道:“大家知道,瑞士是中立國。實際上我的意思是,Arteris是中立的。也就是說,我們自己不設計生產任何芯片,而是為所有的網絡芯片設計公司提供互聯IP,且與任何協議無關。雖然他們是競爭關系,但我們是中立的。”

這時,現場響起一片會意的笑聲。

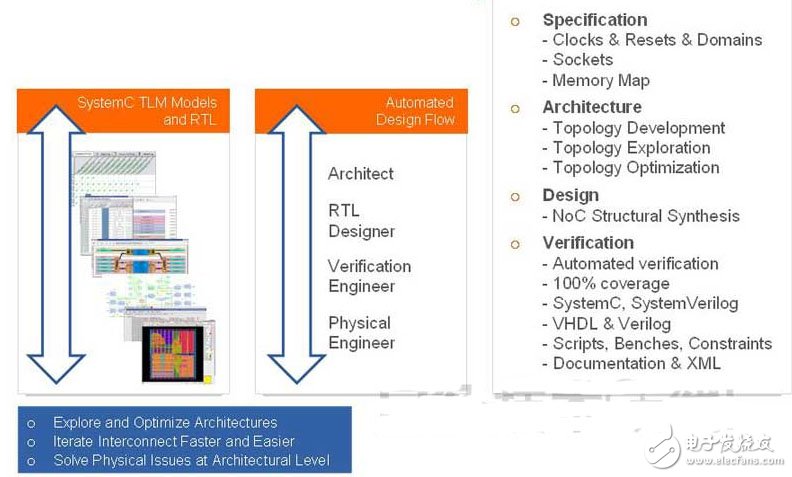

他強調,Arteris的NoC互連IP技術可把用戶通常12~18個月的設計周期縮短到9~12個月(見圖4)。同時,NoC互連工具還可提升SoC的生產力(見圖5)。

圖4 Arteris的NoC互連IP技術可將設計周期縮短為9~12個月

圖5 NoC互連工具可提升SoC的生產力

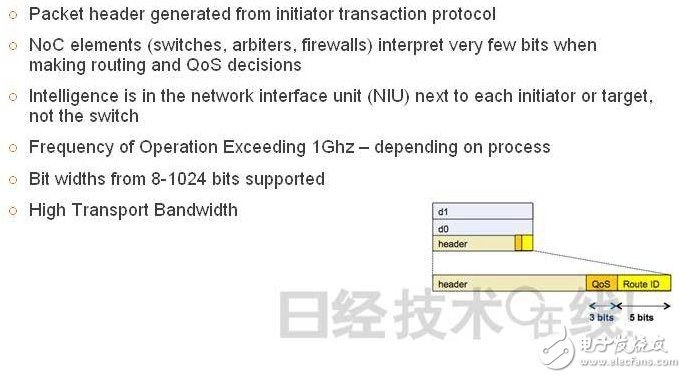

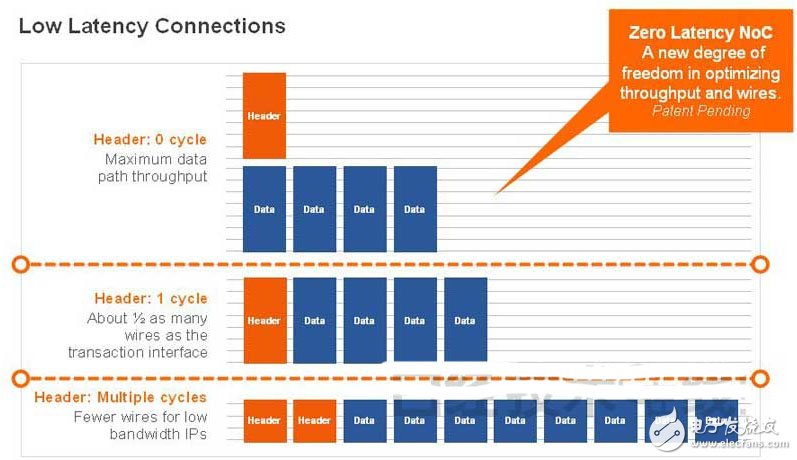

具體地,NoC互連IP技術的工作頻率可達1GHz以上(見圖6),支持CPU到存儲器的高速數據傳輸;極低的連接延遲(見圖7);易于布局布線等。

圖6 NoC互連IP技術支持1GHz以上的工作頻率和高傳輸帶寬

圖7 NoC互連IP技術具有極低的連接延遲特性

此外,與傳統的混合總線互連架構比,NoCIP架構的線路量少了50%,最高工作頻率也高于后者,帶寬提高了1倍,可連接上百個IP塊,功耗不到1W,延遲特性相當甚至更好。

Shuler表示,目前有56個用戶,85項流片及44個完整的芯片設計,用戶的芯片發貨量已達1億多片。

開辟一個嶄新的半導體市場

相比模擬、電源和分立器件300億美元以上的市場,FPGA和可編程微控制器分別有50多億和90多億美元的市場,Silego所在的可配置混合信號芯片(CMIC)市場潛在容量只有30億美元左右。

不過,Silego營銷副總裁John McDonald(見圖8)表示,可配置混合信號芯片或稱“可編程模擬技術”開辟了一個嶄新的半導體“藍海”市場,正因為如此,這個市場的競爭不像前幾個市場那樣激烈。消費類、計算、通信和工業領域的廣泛應用需求正推動這個市場呈現出爆炸式增長的態勢。

圖8 Silego營銷副總裁John McDonald

Silego包括混合信號陣列GreenPAK、電源管理芯片GreenFET、定時產品GreenCLK和接口ASSP在內的4類芯片,近4年內的總出貨量已過10億,2012和2013年的出貨量更是分別達到了2.7億和4.2億。

目前最小的GreenPAK3采用1.6 mm x1.6 mm X0.55mm,12引腳STQFN封裝,其厚度比1美分硬幣還薄(見圖9)。在這樣小的芯片內,集成了模擬元件、數字邏輯、可編程互連架構、I/O及非易失性存儲器等。主要可用于替代4~8位MCU、膠合邏輯、電平轉換器和電壓監控器等。“工程師用所提供的GPAK開發工具,在幾分鐘內就可搞定所需的配置和編程。”McDonald表示。

圖9 GreenPAK3采用1.6x1.6mm212引腳STQFN封裝,厚度比1美分硬幣還薄。

GreenPAK3低成本、低功耗的特點,有助于在可穿戴設備、移動終端及PC市場上,實現差異化設計和產品快速上市。

另外,McDonald透露,Silego在中國設有一個研發中心。計劃在2014年推出8款新產品,同時,將進一步加強與英特爾和nVidia的合作關系。

EDA篇

本次硅谷之行的第三天,筆者又見到了老朋友,Mentor董事會主席兼CEO Walden C. Rhines(見圖1)。這次,有著數十年資深技術背景的Walden既沒有談具體EDA技術,也沒有講市場,而是回顧了EDA驗證的歷史變遷。

圖1 Mentor董事局主席兼CEO Walden C. Rhines(右),副總裁兼設計驗證技術部總經理John Lenyo(左)

邁入驗證3.0時代

在早期的中小規模(SSI/MSI)集成電路設計和驗證中,基本靠設計師手工設計和布局,然后是架構、測試、重復設計,直至項目完成。

1973年4月12日,美國加州大學伯克利分校電子工程系電工實驗室的L.W.Nagel和D.O.Pederson,開發出了電路仿真軟件SPICE。借助這款軟件,設計師可快速可靠地驗證電路設計并預測電路性能。

隨著10萬門以上大型設計對仿真的需求,1982年,Mentor開發出了基于IDEA工作站的QiuickSim數字電路仿真器。

Walden把這個時期稱為“驗證0.0時代”。

此后,便進入了寄存器傳輸級描述的“驗證1.0時代”。這個時期的設計特點是,更加關注描述語言及性能提升。

代表性語言是VHDL。1981年,美國國防部提出了VHSIC語言。1983年,IBM、TI及Intermetrics獲得了相關開發合同。1987年,VHDL被確定為IEEE1076標準語言。

1984年,GateWay設計自動化公司的Phil Moorby創建了Verilog HDL語言。1989年,GateWay被Cadence***。1995年,Verilog成為IEEE1364標準語言。

另外,RTL加速仿真提升了硬件性能。

接著,芯片設計又進入了更加關注方法學的測試平臺(testbench)自動化“驗證2.0時代”。2002年,SystemVerilog語言出現。

Walden稱,他曾在2004年設計自動化大會(DAC)的CEO圓桌論壇上與新思(Synopsys)CEO Aart de Geus的激辯中,力挺SystemVerilog,并提出業界應該創建一個SystemVerilog的設計環境。令他欣慰的是,同年,SystemVerilog被批準為IEEE1800標準語言。

目前,在10多億美元的驗證市場上,SystemVerilog已成為測試平臺主流驗證語言,且遠高于VHDL、System和C/C++等。

企業級驗證平臺

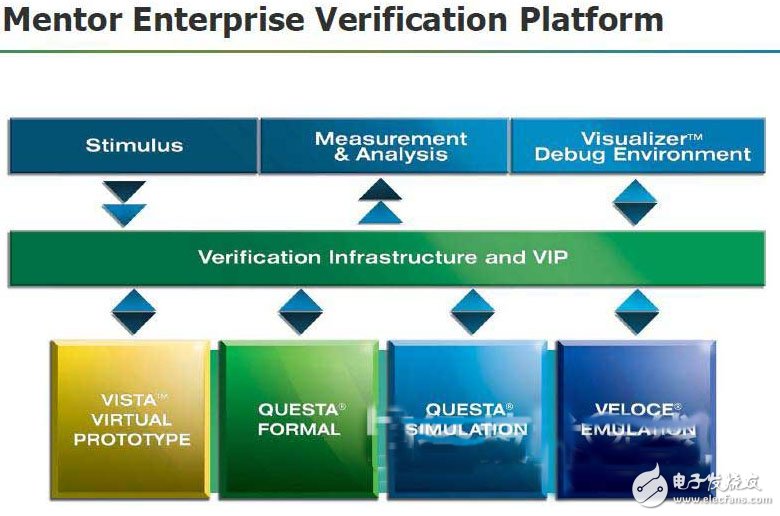

Mentor副總裁兼設計驗證技術部總經理John Lenyo(見圖1)對2014年6月即將上市的企業驗證平臺(EVP)進行了詳細闡述。EVP結構示意圖如圖2所示。

圖2 Mentor的企業級驗證平臺(EVP)

該驗證平臺包括:①仿真加速操作系統Veloce OS3、②統一的硬件調試環境Visualizer、③軟件調試器Codelink,④支持Questa和Veloce的驗證IP。因此,可形成全球范圍的資源數據中心(見圖3)。

圖3 Mentor數據中心里的容納幾十臺Veloce仿真加速器的機柜

①Veloce OS3支持低功耗的UPF驗證;SystemVerilog功能覆蓋率和基于斷言的驗證;及SystemVerilog、UVM和C/C++測試平臺。具有高覆蓋率收斂流程,并進行應用程序軟件關鍵的SoC子系統的流片前性能分析。為了最大程度地復用驗證平臺,按照UVM/RTL標準,為仿真和加速模式專門設計了驗證IP。在保證功能的前提下,可比單獨仿真性能提高1000倍(見圖4)。

圖4 Veloce OS3可加速現有的仿真驗證環境

可用虛擬環境取代實際硬件。PCIe、以太網和USB等標準接口,都可在工作站中實現虛擬化。

隨著復雜度更高的SoC設計項目的增加,例如,系統中含有多個嵌入式內核、異構處理器、復雜的系統內部互連、存儲器共享、片上網絡及多級緩存,“芯片開始驗證轉向系統級驗證,側重于軟硬件協同驗證的設計終于邁入了‘驗證3.0時代’”。 Walden指出。

隨著工藝節點的發展,嵌入式軟件工程師激增,16nm工藝時代是90nm時的17倍。同時,處理器的工作頻率也達3GHz以上。

對于系統及驗證,仿真更是必須。而驗證的關鍵是軟硬件協同。仿真也需從設計師的實驗室轉向數據中心。

Walden表示,驗證3.0時代需要企業級的解決方案,包括調試、驗證IP、用戶接口、測試平臺仿真、斷言及覆蓋。

Veloce OS3 VirtuaLAB外圍設備是立即可重配的,可支持世界各地的多個項目團隊。OS3企業服務器能夠有效地管理全球硬件仿真加速器資源,并將其導入商業隊列管理器中,形成單一的高容量實體。企業服務器決定著每項工作的優先順序,迅速切換優先項目。

②有了SoC設計軟件,設計團隊就可將大部分驗證時間用于調試。因此,提高從模塊到系統的調試效率十分重要。Visualizer調試器、仿真和硬件加速器具備處理現有最大SoC的容量和性能。Visualizer調試器提供了高效的RTL、門級和測試平臺的調試,包括自動追蹤以快速精確定位出錯誤的根本原因,協議和事務級調試,自帶的UVM和SystemVerilog基于類的調試功能,及低功耗UPF調試。仿真和硬件加速的交互模式和后仿真模式也具有上述功能。

③在具備啟動OS的功能后,SoC簽發(signoff)解決方案才得以完善。軟件調試操作系統時,往往需要較多的思考時間,而硬件加速器處于空閑狀態。OS3將思考時間轉移到Codelink工具上,Codelink工具最多可同時支持10個設計師進行JTAG調試,且回放軟件執行速度為100MHz。借助OS3,硬件加速器可以全速執行各任務,而軟件進行離線調試。上述功能可在設計周期中最大程度地提高調試效率,并盡可能早地啟動OS。

④驗證IP支持Questa和Veloce,具有共同的仿真驗證和測試平臺特性,軟件可移植,測試環境可重用(見圖5)。

圖5 驗證IP具有測試平臺可移植性

許多 SoC項目的驗證數據有多個來源,需對驗證數據合并與綜合分析,以評估實際項目的完成情況。Veloce OS3 和Questa 10.3可將所有斷言、覆蓋率和運行時間數據,包括硬件仿真、形式驗證、仿真、混合信號和低功耗等,寫入共同數據庫。借助共同數據庫、Questa驗證管理工具和測試計劃,驗證小組能夠立即查看覆蓋率情況,準確查出無效測試,縮短數據合并時間,提高回歸測試的吞吐率,減少調試時間,從總體上提高產品質量和生產率。

EVP 統一覆蓋數據庫 (UCDB)支持統一覆蓋互通性標準(UCIS),在了解其它驗證引擎已取得的覆蓋率的情況下,優化下載到硬件加速器的邏輯的覆蓋率,縮短編譯時間,節約硬件仿真資源,創建更智能的覆蓋率收斂流程。

最后,Lenyo總結指出,實際上,企業驗證平臺就是把虛擬原型、架構分析和軟硬件加速仿真結合在一起,使從最初設計創意、硅片制造到成品的整個驗證過程均從基本驗證引擎中提取出來。

?

電子發燒友App

電子發燒友App

評論