您的位置:電子發燒友網 > 電子技術應用 > 測量儀表 > 可靠性分析 >

深亞微米CMOS IC全芯片ESD保護技術

2012年03月27日 16:27 來源:本站整理 作者:秩名 我要評論(0)

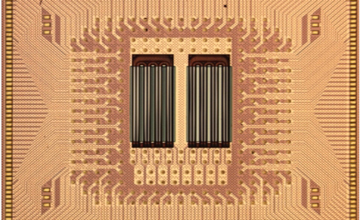

摘 要:CMOS工藝發展到深亞微米階段,芯片的靜電放電(ESD)保護能力受到了更大的限制。因此,需要采取更加有效而且可靠的ESD保護措施。基于改進的SCR器件和STFOD結構,本文提出了一種新穎的全芯片ESD保護架構,這種架構提高了整個芯片的抗ESD能力,節省了芯片面積,達到了對整個芯片提供全方位ESD保護的目的。

1 引言

靜電放電保護對于深亞微米設計來說,由于柵氧薄、溝道短、源漏結淺再加上輕摻雜漏(LDD)以及硅化物擴散等工藝,使得傳統的ESD保護電路保護能力降低。所以深亞微米CMOS IC的ESD保護變得更加困難。在考慮提高IC ESD保護能力的同時,又要盡可能減少保護電路所占的版圖面積,這在多管腳CMOS電路中,問題尤為突出。

傳統上,為加強ESD保護能力,大都僅在輸入PAD附近做上ESD保護電路。大量的實驗結果表明,即使在輸入與輸出PAD上已有適當的ESD保護電路,仍然出現CMOS IC的內部電路因ESD測試而發現異常的損傷問題。因此,ESD的保護設計必須要注意全芯片(whole-chip)保護架構的設計,才能夠真正避免內部電路發生異常損傷的問題。

ESD事件可以在CMOS芯片上各種引腳(輸入PAD、輸出PAD、VDD和VSS)之間以各種組合隨機發生,所以,在CMOS芯片各PAD外圍都必須有相應的ESD保護電路,而且該保護電路對各種可能發生的ESD組合都要有很好的保護作用。另一方面,輸入輸出PAD之間的ESD事件時常會發生ESD電壓轉而跨在VDD與VSS電源線之間,造成IC內部電路損傷導致VDD對VSS的漏電增加,甚至永久短路。在深亞微米CMOS IC中,這種破壞現象尤其常見。

針對這些問題,結合實際工作,本文以改進的SCR器件和STFOD結構為基礎,提出了一種新穎的全芯片ESD保護架構,這種架構不僅提高了整個芯片的抗ESD能力,而且節省了芯片面積,達到了對整個芯片提供全方位ESD保護的目的。

2 互補式LVTSCR器件在輸入級ESD保護電路中的應用

2.1 ESD應力模式

ESD電壓對于VDD和VSS節點來說可以分別是正或負極,所以對每個管腳來說,都有四種ESD應力模式。

(1)PS-mode(Pin-to-VSS正極性):VSS腳接地,正的ESD電壓出現在該I/O腳對VSS腳放電時,此時VDD與其他腳懸空。

(2)Ns-mode(Pin-to-VSS負極性):VSS腳接地,負的ESD電壓出現在該I/O腳對VSS腳放電時,此時VDD與其他腳懸空。

(3)PD-mode(Pin-to-VDD正極性):VDD腳接地,正的ESD電壓出現在該I/O腳對VDD腳放電時,此時VSS與其他腳懸空。

(4)ND-mode(Pin-to-VDD負極性):VDD腳接地,負的ESD電壓出現在該I/O腳對VDD腳放電時,此時VSS與其他腳懸空。

芯片輸入輸出腳的ESD耐壓度是以以上四種ESD放電組合模式下最低的耐壓值為判定值。先前的ESD保護設計中,LVTSCR器件只被安放在PAD到VSS的放電路徑上,也就是說該LVTSCR器件只被用來提升PS-mode的.ESD保護能力,不能提供對PAD全方位的保護。

2.2 互補式LNTSCR在輸出級:ESD保護電路中的應用

在圖1中顯示了一種互補式LVTSCR的靜電放電保護電路。在該電路中有兩個LVTSCR器件,其中LVTSCR2被安排在PAD到VSS之間用來保護PS-mode的ESD放電,此LVTSCR2是在SCR器件中內嵌一NMOS器件而成的;另外有一LVTSCR1器件被安排在PAD到VDD之間,用來保護ND-mode的ESD放電,此LVTSCR1器件是在SCR器件內嵌一PMOS器件而成的。這LVTSCR1與LVTSCR2正好形成互補式(Complementary)的結構,可以有效地提升該PAD的ESD保護能力。另外NS-mode的ESD放電,被D1二極管旁通掉;PD-mode的ESD放電被D2二極管旁通掉。在圖1所示的互補式LVTSCR ESD保護電路中,四個不同的放電組合都被一對一地保護著,故可以真正地提供全方位的ESD保護能力。另外,由于LVTSCRl內嵌的PMOS柵極接到VDD,所以LVTSCR1在CMOS IC正常工作情形下是關閉的,只有當ESD放電時才會被導通,此LVTSCR1的導通電壓等效于PMOS的驟回擊穿(Snap shoot)電壓(約-10~15V)。試驗證明,在較小的面積下,該互補LVTSCR電路能承受更高的ESD電壓(》8000V)

3 HINSCR和HIPSCR器件在輸出級ESD保護電路中的應用

圖2所示HINTSCR是將一旁通二極管:Dp2埋入一N型LVTSCR器件而形成的一種高電流低電壓NMOS觸發的橫向SCR器件,HIPTSCR將一旁通二極管。Dn2埋人一P型的LVTSCR器件中而形成的高電流低電壓PMOS觸發的橫向SCR器件。這兩個器件可以與集成電路的輸出級PMOS器件與NlMOS器件合并在版圖中,以提升該輸出級的靜電放電保護能力。此特別埋入的二極管會分流掉一部份觸發電流,因此}IINTSCR器件與HIPTSCR器件必須要有更大的外界觸發電流才會被觸發導通,改變二極管在該HINTSCR器件與HIPTSCR器件結構內的面積大小即可設計出不同觸發電流的HINTFSCR器件與HIPTSCR器件。HINTSCR器件和HIPTSCR器件的ESD保護能力與前述互補LVTSCR器件相同,此處不再贅述。值得一提的是,該保護電路具有極高的抗噪聲干擾能力,因此更適合于輸出級:ESD保護電路。圖2是其應用在集成電路輸出級的等效電路圖。

本文導航

- 第 1 頁:深亞微米CMOS IC全芯片ESD保護技術(1)

- 第 2 頁:基于STFOD結構的ESD偵測電路

- 第 3 頁:VDD加電情形