完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網技術文庫為您提供最新技術文章,最實用的電子技術文章,是您了解電子技術動態的最佳平臺。

雖然DUVL機器可以通過多重曝光技術將線寬縮小到7-5納米,但如果要獲得更小的線寬,DUVL已經達到了極限。采用EUV作為光源的極紫外光刻(EUVL)成為研究的重點,其波長為13.5納米。...

在半導體工藝中,“鍵合”是指將晶圓芯片連接到襯底上。粘接可分為兩種類型,即傳統方法和先進方法。傳統的方法包括晶片連接(或晶片連接)和電線連接,而先進的方法包括IBM在60年代末開發的倒裝芯片連接。...

晶圓測試的對象是晶圓,而晶圓由許多芯片組成,測試的目的便是檢驗這些芯片的特性和品質。為此,晶圓測試需要連接測試機和芯片,并向芯片施加電流和信號。...

PDK 提供了開發平面芯片所需的適當詳細程度,將設計工具與制造工藝相結合,以實現可預測的結果。但要讓該功能適用于具有異構小芯片的PDK,要復雜很多倍。...

CP(Chip Probing)測試也叫晶圓測試(wafer test),也就是在芯片未封裝之前對wafer進行測試,這樣就可以把有問題的芯片在封裝之前剔除出來,節約封裝和FT的成本。...

凸點金屬化是為了將半導體中P-N結的性能引出,其中熱壓倒裝芯片連接最合適的凸點材料是金,凸點可以通過傳統的電解鍍金方法生成,或者采用釘頭凸點方法,后者就是引線鍵合技術中常用的凸點形成工藝。...

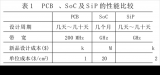

WLP 可以有效提高封裝集成度,通常采用倒裝(FC)互連技術,是芯片尺寸封裝 CSP 中空間占用最小的一種。...

WAT需要標注出測試未通過的裸片(die),只需要封裝測試通過的die。 FT是測試已經封裝好的芯片(chip),不合格品檢出。WAT和FT很多項目是重復的,FT多一些功能性測試。WAT需要探針接觸測試點(pad)...

在自然界中,獲取成本最低的半導體就是硅。而硅料的提取是熔煉砂子。提到這里可能有朋友想到“光伏電池片用的也是硅片”。...

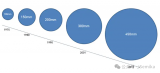

先看一些晶圓的基本信息,和工藝路線。 晶圓主要尺寸有4吋,6吋硅片,目前對8吋,12吋硅片的應用在不斷擴大。這些直徑分別為100mm、150mm、200mm、300mm。硅片直徑的增大可降低單個芯片的制造成本。...

封裝的主要生產過程包括:晶圓切割,將晶圓上每一晶粒加以切割分離。粘晶,(Die-Attach)將切割完成的晶粒放置在導線架上。焊線,(WireBond)將晶粒信號接點用金屬線連接至導線架上。...

用于定義晶圓表面特性的 TTV、彎曲和翹曲術語通常在描述晶圓表面光潔度的質量時引用。首先定義以下術語以描述晶圓的各種表面。...

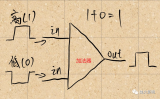

目前最先進的黃光微影制程中,使用ArF準分子雷射(λ=193nm)作為光源。nm為nano-meter,代表10的負九次方。...

當等離子體轉變到這種狀態時,電子密度處于最低水平。一般來說,等離子體密度下降的水平取決于占空比和脈沖頻率。通過調整脈沖的占空比,可以將時間平均離子能量分布函數進行調整。...

封裝可行性審查應在封裝開發初期進行,審查結果需要提交給芯片和產品設計人員做進一步反饋。完成可行性研究后,須向封裝制造商下訂單,并附上封裝、工具、引線框架和基板的設計圖紙。...

在多層集成電路中,薄的、短的局部互連提供片上連接,而厚的、長的全局互連在不同的塊之間傳輸。正如Lam Research技術總監Larry Zhao所詳細描述的那樣,硅通孔(TSV)允許信號和功率從一層傳輸到下一層。...

隨著晶體管尺寸的逐步縮小,其特征尺寸也在不斷縮小,當特征尺寸到了22nm,平面晶體管由于其柵極對于溝道的控制能力較弱而出現短溝道效應,逐漸被一種新型的晶體管所取代,即鰭式場效應晶體管(Fin FET)。...