您的位置:電子發(fā)燒友網(wǎng) > 電子技術(shù)應(yīng)用 > 電源管理 > 開關(guān)電源 >

由開關(guān)電源驅(qū)動(dòng)的高速ADC設(shè)計(jì)

2012年05月06日 11:20 來源:本站整理 作者:秩名 我要評論(0)

系統(tǒng)設(shè)計(jì)人員正面臨越來越多的挑戰(zhàn),他們必須在不降低系統(tǒng)元件(如高速資料轉(zhuǎn)換器)性能的情況下讓設(shè)計(jì)最大程度地實(shí)現(xiàn)節(jié)能。設(shè)計(jì)人員們可能轉(zhuǎn)而採用許多以電池供電的應(yīng)用(如某種手持終端、軟體無線設(shè)備或可攜式超音波掃描器),也可能縮小產(chǎn)品的外形尺寸,因而必須尋求減少發(fā)熱的諸多方法。

極大降低系統(tǒng)功耗的一種方法是對高速資料轉(zhuǎn)換器的電源進(jìn)行最佳化。資料轉(zhuǎn)換器設(shè)計(jì)和製程技術(shù)的一些最新進(jìn)展,讓許多新型ADC可直接由開關(guān)電源來驅(qū)動(dòng),因而達(dá)到最大化功效的目的。

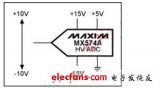

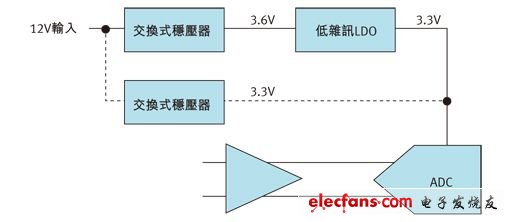

系統(tǒng)設(shè)計(jì)人員們習(xí)慣在交換式穩(wěn)壓器和ADC之間使用一些低雜訊、低壓降穩(wěn)壓器(LDO),以清除輸出雜訊和開關(guān)頻率突波(請參見圖1)。但是,這種乾凈的電源設(shè)計(jì)代價(jià)是高功耗,因?yàn)長DO要求壓降余量來維持正常的執(zhí)行。最低壓降一般為200到500mV,但在一些系統(tǒng)中則可高達(dá)1到2V(例如,ADC的3.3V電壓軌產(chǎn)生自一個(gè)使用LDO的5V開關(guān)電源時(shí))。

圖1:從傳統(tǒng)電源轉(zhuǎn)到最大功效電源。

就一個(gè)要求3.3V電壓軌的資料轉(zhuǎn)換器而言,300mV的LDO壓降增加約10%的ADC功耗。這種效應(yīng)在資料轉(zhuǎn)換器中更加顯著,因?yàn)樗哂懈〉难u程節(jié)點(diǎn)和更低的電源電壓。例如,1.8V時(shí),相同300mV壓降增加約17%(300mV/1.8V)的ADC功耗。因此,將該鏈路的低雜訊LDO去除可產(chǎn)生巨大的節(jié)能效果。去除LDO還可以降低設(shè)計(jì)板級空間、熱量以及成本。

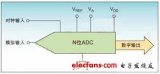

本文闡述包括超高性能16位元ADC在內(nèi)的一些TI高速ADC可在ADC性能無明顯降低的條件下直接透過交換式穩(wěn)壓器驅(qū)動(dòng)。為了闡述的方便,我們對兩款不同的資料轉(zhuǎn)換器(一款使用高性能BiCOM技術(shù)(ADS5483),另一款使用低功耗CMOS技術(shù)(ADS6148),以進(jìn)行開關(guān)電源雜訊的感應(yīng)性研究。本文的其他部份對所得結(jié)果分別進(jìn)行介紹。

採用BiCOM技術(shù)的ADC

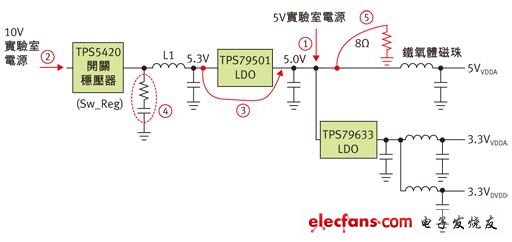

這種製程技術(shù)實(shí)現(xiàn)寬輸入頻率範(fàn)圍下的高訊號雜訊比(SNR)和高無突波動(dòng)態(tài)範(fàn)圍(SFDR)。BiCOM轉(zhuǎn)換器一般還具有許多晶片去耦電容器和非常不錯(cuò)的電源抑制比(PSRR)。我們對ADS5483評估板(ADS5483EVM)進(jìn)行了電源研究,其具有一個(gè)使用TPS5420交換式穩(wěn)壓器(Sw_Reg)的板上電源;一個(gè)低雜訊LDO(TPS79501);以及一個(gè)外部實(shí)驗(yàn)室電源使用選項(xiàng)。我們使用圖2所示不同結(jié)構(gòu)實(shí)施了5次實(shí)驗(yàn),旨在確定ADS5483透過一個(gè)交換式穩(wěn)壓器直接執(zhí)行時(shí)出現(xiàn)的性能降低情況。由于ADS5483類比5V電源到目前為止表現(xiàn)出對電源雜訊的最大感應(yīng)性,因此該研究忽略了3.3V電源的雜訊。ADS5483產(chǎn)品說明書中列出的PSRR支援這種情況:兩個(gè)3.3V電源的PSRR至少高出5V類比電源20dB。

圖 2:使用ADS5483EVM的5次實(shí)驗(yàn)電源結(jié)構(gòu)。

5次實(shí)驗(yàn)的結(jié)構(gòu)變化配置如下:

實(shí)驗(yàn) 1:

一個(gè)5V實(shí)驗(yàn)室電源直接連接到5-V類比輸入,同時(shí)繞過交換式穩(wěn)壓器(TPS5420)和低雜訊LDO(TPS79501)。使用一個(gè)板上LDO(TPS79633)產(chǎn)生ADS5483低感應(yīng)度3.3V類比及數(shù)位電源的3.3V電壓軌。

實(shí)驗(yàn)2

將一個(gè)10V實(shí)驗(yàn)室電源連接到TPS5420降壓穩(wěn)壓器,其使用一個(gè)5.3V輸出。這樣可為TPS79501提供一個(gè)300mV 壓降,因而產(chǎn)生一個(gè)5V電壓軌。

實(shí)驗(yàn)3

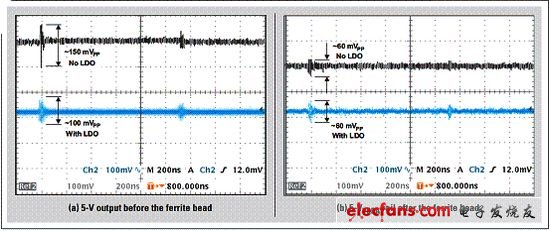

使用TPS5420,從10V實(shí)驗(yàn)室電源產(chǎn)生一個(gè)5V電壓軌。本實(shí)驗(yàn)中,我們繞過了TPS79501低雜訊LDO。圖3a顯示,如‘實(shí)驗(yàn)2’連接的LDO較好地減少了交換式穩(wěn)壓器的5.3V輸出峰值電壓。但是,圖3b顯示5VVDDA電壓軌鐵氧體磁珠之后輸出沒有巨大的差異。

圖3:實(shí)驗(yàn)2(使用LDO)和實(shí)驗(yàn)3(無LDO)的示波器截圖對比。

實(shí)驗(yàn) 4

本實(shí)驗(yàn)配置方法與‘實(shí)驗(yàn)3’相同,但去除了TPS5420輸出的RC緩衝器電路,其會(huì)引起高振鈴和大開關(guān)頻率突波。

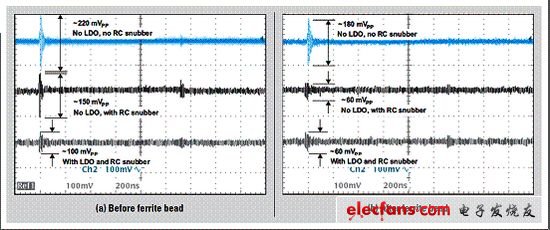

我們可在圖4中清楚的觀察到RC緩衝器電路的影響。去除LDO并沒有在鐵氧體磁珠之后表現(xiàn)出明顯的差異,而去除RC緩衝器電路則會(huì)導(dǎo)致更大的清潔5VVDDA 電壓軌電壓峰值進(jìn)入ADC。我們將在稍后詳細(xì)研究RC緩衝器電路的影響。

圖4:5VVDDA電壓軌的電源雜訊。

實(shí)驗(yàn) 5

將一個(gè)8Ω功率電阻連接到5V電源,類比如現(xiàn)場可程式設(shè)計(jì)閘陣列(FPGA)等額外負(fù)載。TPS5420必須提供更高的輸出電流,并更努力地驅(qū)動(dòng)其內(nèi)部開關(guān),因而產(chǎn)生更大的輸出突波。通過重復(fù)進(jìn)行‘實(shí)驗(yàn)2’、‘實(shí)驗(yàn)3’和‘實(shí)驗(yàn)4’可以測試這種配置。

本文導(dǎo)航

- 第 1 頁:由開關(guān)電源驅(qū)動(dòng)的高速ADC設(shè)計(jì)(1)

- 第 2 頁:測量結(jié)果

- 第 3 頁:采用CMOS技術(shù)的ADC

- 第 4 頁:測量結(jié)果

標(biāo)簽:開關(guān)電源(826)ADC(546)高速ADC(20)

用戶評論

發(fā)表評論

開關(guān)電源業(yè)界動(dòng)態(tài)

開關(guān)電源技術(shù)應(yīng)用

開關(guān)電源資料下載

- 劉勝利現(xiàn)代高頻開關(guān)電源實(shí)用技術(shù).pdf

- 開關(guān)電源的有源功率因數(shù)校正電路設(shè)計(jì)方案

- 開關(guān)電源設(shè)計(jì)與計(jì)算

- 開關(guān)電源設(shè)計(jì)與原理

- 解讀開關(guān)電源難點(diǎn)問題

- 基于開關(guān)電源的無線智能家居控制系統(tǒng)

- 開關(guān)電源設(shè)計(jì)__第二版_Switching_Power_Supply_Design__Second_Edition_(全

- “開關(guān)電源電路設(shè)計(jì)要點(diǎn)與調(diào)試”技術(shù)講座視頻下載

- 反激式開關(guān)電源變壓器設(shè)計(jì)方案

- 開關(guān)電源電路設(shè)計(jì)要點(diǎn)與調(diào)試-電子發(fā)燒友網(wǎng)講座資料

ADC技術(shù)應(yīng)用

ADC資料下載

- MAX1302英文數(shù)據(jù)資料

- 流水線ADC的行為級仿真

- 校準(zhǔn)ADC內(nèi)部偏移的光學(xué)微控制器DS4830

- 利用過采樣技術(shù)提高ADC測量分辨率

- ADC模數(shù)轉(zhuǎn)換器有效位計(jì)算

- ADC需要考慮的交調(diào)失真因素

- 簡單的多輸出范圍16位DAC設(shè)計(jì)

- MAX11120-MAX11128 1Msps, Low-Power, Serial Channel ADC

- STC12C5A60S2系列ADC測試結(jié)果(使用12位DA測試--4096個(gè)測試點(diǎn))

- ADC簡化測量高阻抗傳感器