您的位置:電子發燒友網 > 電子技術應用 > 電源管理 > 開關電源 >

由開關電源驅動的高速ADC設計(3)

2012年05月06日 11:20 來源:本站整理 作者:秩名 我要評論(0)

采用CMOS技術的ADC

當關注如何在保持較佳的SNR和SFDR性能的同時也盡可能地降低功耗時,我們一般利用CMOS技術來開發高速資料轉換器。但是,CMOS轉換器的PSRR一般并不如BiCOM ADC的好。ADS6148產品說明書列出了25dB的PSRR,而在類比輸入電源軌上ADS5483的PSRR則為60dB。

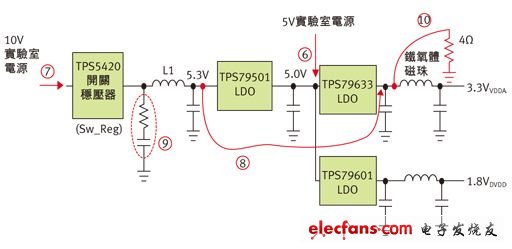

ADS6148EVM使用一種板上電源,其由一個交換式穩壓器(TPS5420)和一個低雜訊、5V輸出LDO(TPS79501)組成,后面是一些3.3V和1.8V電源軌的低雜訊LDO(請參見圖10)。與使用ADS5483EVM的5個實驗類似,我們使用ADS6148EVM進行了下面另外5個實驗,其注意力只集中在3.3VVDDA電壓軌的雜訊上面。1.8VDVDD電壓軌外置TPS5420實驗顯示對SNR和SFDR性能沒有什么大的影響。

圖10:使用ADS6148EVM的5個實驗電源結構。

實驗6

將一個5V實驗室電源連接到兩個低雜訊LDO(一個使用3.3V輸出,另一個使用1.8V輸出)的輸入。LDO并未對實驗室電源帶來任何有影響的雜訊。

實驗7

將一個10V實驗室電源連接到TPS5420降壓穩壓器,其與一個5.3V輸出連接,像‘實驗2’連接ADS5483一樣。TPS79501產生了一個過濾后的5.0V電壓軌,對于3.3V輸出和1.8V輸出LDO提供輸入,如圖10所示。

實驗8

所有3.3VVDDA電壓軌LDO均被加以旁路。TPS5420配置為一個3.3V輸出,該輸出直接連接到3.3VVDDA電壓軌。TPS79601產生1.8VDVDD電壓軌,并透過一個外部5V實驗室電源供電。

實驗9

該實驗配置方法與‘實驗8’相同,但去除了TPS5420輸出的RC緩衝器電路。

實驗10

一個4Ω功率電阻連接到TPS5420的3.3V輸出。這樣做可大幅增加TPS5420的輸出電流,因而類比一個附加負載。另外,像‘實驗5’的ADS5483一樣,它帶來了更高的開關突波和更多的振鈴。

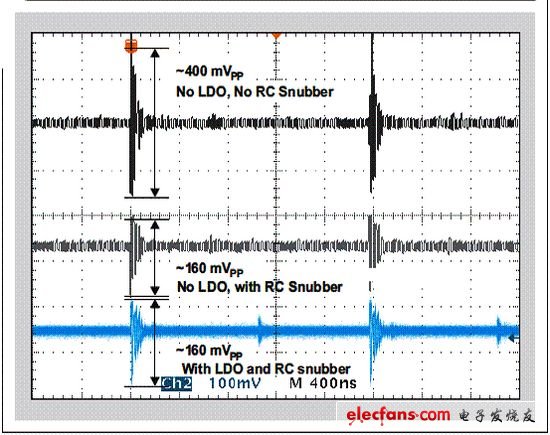

圖11顯示了‘實驗7’、‘實驗8’和‘實驗9’產生的一些3.3VVDDA 輸出波形。有或無LDO的峰值電壓振幅存在一些差異,但RC緩衝器可降低60%的峰值雜訊。

圖11:鐵氧體磁珠后測得3.3VVDDA 電壓軌實驗示波器截圖對比。

本文導航

- 第 1 頁:由開關電源驅動的高速ADC設計(1)

- 第 2 頁:測量結果

- 第 3 頁:采用CMOS技術的ADC

- 第 4 頁:測量結果