跨時鐘域電路設計:單周期脈沖信號如何跨時鐘域

參數REG_OUTPUT用于確定是否對最終輸出信號寄存;參數RST_USED用于確定是否使用復位信號....

單位寬信號如何跨時鐘域

單位寬(Single bit)信號即該信號的位寬為1,通常控制信號居多。對于此類信號,如需跨時鐘域可....

FPGA設計中的反饋路徑可以怎么優化呢?

在FPGA設計中,我們可能會碰到這樣的路徑,如下圖所示。圖中兩個輸入數據為64位,寄存一拍后給到二選....

基于20nm工藝制程的FPGA—UltraScale介紹

UltraScale是基于20nm工藝制程的FPGA,而UltraScale+則是基于16nm工藝制....

基于28nm工藝制程的7系列FPGA

7系列FPGA是基于28nm工藝制程。在7系列FPGA中,每個輸入/輸出區域(I/O Bank)包含....

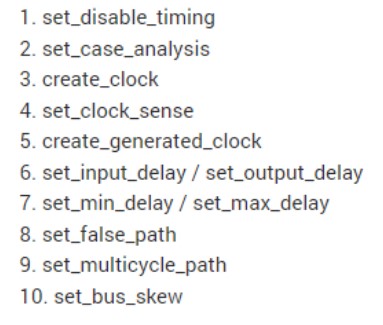

縮短Vivado編譯時間之審視時序約束描述

在描述時序約束時,一個重要的原則是確保約束簡潔高效。簡潔高效意味著約束只針對指定的對象,即約束對應的....

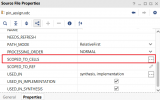

Vivado里如何手動調整編譯順序

通常情況下,一旦創建好Vivado工程,添加了相應的RTL文件,Vivado會自動找到設計的頂層文件....

關于Vivado Non-project,我們應知道的一些問題

Vivado支持Project模式也支持Non-Project模式。兩者既可以支持圖形界面也支持Tc....

理解Vitis HLS默認行為

相比于VivadoHLS,Vitis HLS更加智能化,這體現在Vitis HLS可以自動探測C/C....

Vivado里如何使用模糊性的位置約束?

提到位置約束,我們會想到手工布局的方式,即畫Pblock,將指定模塊放入相應Pblock內,這既是面....

如何理解HLS Block-level輸入輸出信號之間的時序關系

默認情況下,VitisHLS會對待綜合的C函數使用ap_ctrl_hs接口,這其實是一種握手方式。在....

用HLS實現PID控制器

PID控制器(比例-積分-微分控制器),由比例單元(Proportional)、積分單元(Integ....

Xilinx推出了新一代功耗評估工具:PDM

PDM支持兩種使用流程:手工流程和導入流程。手工流程要求工程師手動輸入各種參數,如時鐘頻率、翻轉率、....

AIE支持哪兩種類型的RTP

AIE Kernel有時需要由外部提供參數更新kernel行為,此時就要用到RTP(Run-Time....

Vivado Synthesis模塊化的設計方法

全局綜合(Global Synthesis)全局綜合意味著整個設計在一個Synthesis Desi....